Przykład 2 - translator ADG3123

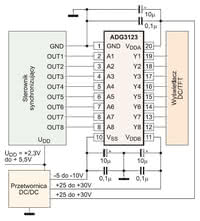

Na rysunku 10 przedstawiono uproszczony schemat funkcjonalny układu ADG3123. Jest to 8-kanałowy translator poziomów logicznych układów CMOS podawanych na wejścia A1- A8 do wyższych napięć, które dostępne są na zaciskach Y1-Y8. ADG3123 jest zasilany ze źródeł napięcia doprowadzonych do zacisków UDDB i USS. Wartości tych napięć ustalają napięcie logicznego poziomu niskiego dla wszystkich wyjść oraz poziomu wysokiego dla wyjść Y7 i Y8.

Napięcie logicznego poziomu wysokiego dla pozostałych wyjść (Y1-Y6) zależy natomiast od wartości napięcia na zacisku UDDA. By translator funkcjonował poprawnie, napięcie UDDB powinno być równe lub większe od napięcia UDDA, z kolei napięcie między zaciskiem UDDB i pinem USS nie powinno przekroczyć 35V. Omawiany translator wykorzystać można na przykład w układach sterujących wyświetlaczami LCD TFT.

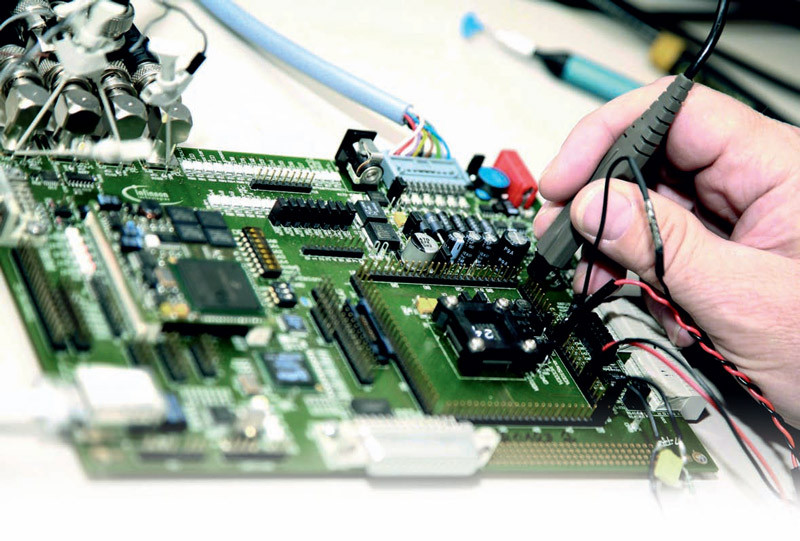

Często sygnały synchronizujące proces skanowania pikseli są do paneli przekazywane za pośrednictwem niskonapięciowych układów CMOS, podczas gdy większość wyświetlaczy pracuje przy wyższych napięciach. Stąd wymagana jest translacja poziomu sygnałów synchronizujących do wartości umożliwiających wysterowanie wyświetlacza. Przykład takiego rozwiązania przedstawia rysunek 11, na którym układ ADG3123 podwyższa napięcia ośmiu sygnałów sterujących.

Przykład 3 - translator ADG3304

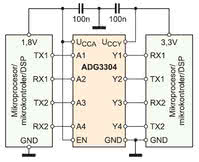

Rys. 13. ADG3304 pośredniczy w transmisji między dwoma procesorami zasilanymi różnymi napięciami, które komunikują się w trybie full-dupleks

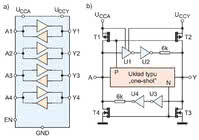

Na rysunku 12 przedstawiono schemat funkcjonalny (a) oraz uproszczony schemat struktury wewnętrznej (b) czterokanałowego dwukierunkowego translatora napięć ADG3304. Translator jest zasilany z dwóch źródeł napięcia podłączanych do zacisków UCCA i UCCY (UCCA powinno być równe lub mniejsze od UCCY), względem których ustalane są napięcia poziomów logicznych na zaciskach odpowiednio A1-A4 oraz Y1-Y4.

W zależności od tego, na które porty doprowadzane są sygnały wejściowe, następuje translacja napięć w kierunku A->Y lub w odwrotnym. W pierwszym przypadku wykorzystywane są bloki U1 oraz U2, natomiast w translacji w kierunku Y->A udział biorą bloki U3 oraz U4. Translator nie wymaga dodatkowego sygnału kontrolnego określającego kierunek translacji.

Częścią ADG3304 jest też układ typu "oneshot", który wykrywa narastające lub opadające zbocza sygnałów wejściowych poszczególnych kanałów, załączając odpowiednio tranzystor PMOS: T1 lub T2 albo jeden z tranzystorów NMOS: T3 lub T4. W ten sposób przyspieszane jest ładowanie lub rozładowywanie pojemności obciążeń pojemnościowych, co skraca czas przejście między poziomami logicznymi.

W opisywanym układzie możliwa jest też jednoczesna translacja napięć w obu kierunkach, tzn. dopuszczalna jest sytuacja, w której na przykład w dwóch kanałach zachodzi konwersja napięć w kierunku A->Y, natomiast w pozostałych w kierunku odwrotnym. Przykład zastosowania tej funkcji translatora przedstawiono na rysunku 13. ADG3304 jest tu wykorzystywany jako układ pośredniczący w komunikacji między dwoma procesorami zasilanymi różnymi napięciami (1,8V i 3,3V), które pracując w trybie full-dupleks transmitują dane przez zaciski TX1/RX1 i TX2/RX2.

Monika Jaworowska