Rosnące wymagania co do minimalizacji mocy pobieranej przez impulsowe zasilacze sieciowe w stanie bez obciążenia to skutek tego, że takich urządzeń jest podłączonych do sieci bardzo dużo. Ładowarki, zasilacze urządzeń RTV i AGD, sprzęt komputerowy, układy domowej automatyki i wiele innych urządzeń nie wyłącza się wcale, nawet gdy nie jest pobierana z nich energia.

Sumarycznie miliony takich zasilaczy pobierają i tracą dużą moc i od kilku lat z tym niekorzystnym zjawiskiem próbuje się walczyć. Najskuteczniejsze są wymagania prawne, związane z dyrektywami Unii Europejskiej w zakresie tzw. ekoproduktu, które określają maksymalną moc standby, jaką mogą pobierać zasilacze.

Co więcej, wymagania te co kilka lat są przesuwane w dół, czyli innymi słowy są one coraz bardziej rygorystyczne. Regulacje w zakresie mocy standby są potrzebne, bo na rynku było wiele kiepskich jednostek zasilających, które nie tylko miały małą sprawność konwersji przy pełnym obciążeniu, a moc standby potrafiła wynosić nawet 30-50% mocy wyjściowej. Spełnienie wymagań norm w zakresie mocy pobieranej bez obciążenia wymaga przede wszystkim użycia nowoczesnego sterownika.

VIPer0P

Układ VIPer0P pobiera maksymalnie 4-10 mW mocy z sieci 230 VAC, na tyle niewiele, że producent zaokrągla wartość tę do zera zgodnie z wytycznymi wyjątku 4.5 normy IEC 62301 w zakresie urządzeń domowych i biurowych. 10 mW pobierane jest w normalnych warunkach, przy braku obciążenia.

Zwarcie z masą specjalnej końcówki wprowadza układ w tryb zero-power (ZPM), gdzie pobierana moc nie przekracza 4 mW. Konstrukcja tego wejścia pozwala na połączenie go z mikrokontrolerem i traktowanie analogicznie do linii shut-down w wielu innych chipach.

VIPer0P może pracować w topologii przetwornicy zaporowej, konwertera obniżającego napięcie lub podwyższająco-obniżającego. W strukturze scalonej zintegrowano 800-woltowy tranzystor mocy MOSFET i maksymalnym szczytowym prądzie 2 A, a więc o wyższym niż dotychczas napięciu przebicia dren-źródło, co pozwala na wykorzystanie słabszych elementów tłumiących przepięcia i tym samym na wzrost sprawności przetwarzania zasilacza.

Jego maksymalna rezystancja w stanie włączenia wynosi 20 Ω. Jest też układ startowy dostarczający zasilania, zanim całość wystartuje, wzmacniacz napięcia błędu, napięcie odniesienia 1,2 V typu bandgap. Co więcej, po uruchomieniu zasilaczy nie ma wymagania co do zapewnienia wydajnego zasilania o większej mocy.

W tym celu wiele zasilaczy wymaga wykonania dodatkowego uzwojenia pomocniczego na transformatorze, skąd czerpana jest energia podczas pracy. Tu nie jest to potrzebne, dzięki czemu realizacja układowa jest prostsza.

Stabilność pracy jest zapewniona poprzez rozdzielenie mas obwodu mocy i sprzężenia zwrotnego, a tranzystor mocy pozwala na kontrolę płynącego prądu (tzw. SenseFET) z ograniczeniem maksymalnej wartości. VIPer0P może być zasilany napięciem z zakresu od 4,5 do 30 V.

Obniżenie mocy pobieranej przez układ bez obciążenia realizuje się przez zmianę modulacji z PWM przy stałej częstotliwości na regulację impulsową ze zmienną częstotliwością i pracę z gubieniem impulsów.

Kolejną ważną funkcją jest oscylator wbudowany w układ, który działa z częstotliwością 60 (wersja L) lub 120 kHz (wersja H), ale dodatkowo widmo jest lekko rozpraszane (±7% z częstotliwością ok. 260 Hz), co ułatwia walkę z kompatybilnością elektromagnetyczną i pozwala na użycie mniejszych i tańszych filtrów sieciowych.

Funkcjonalność układu determinują układ płynnego startu, zabezpieczenia przed przeciążeniem i zwarciem (OLP), ograniczenie maksymalnej dopuszczalnej wartości współczynnika wypełnienia, która zapobiega niekontrolowanemu wzrostowi napięcia na zaciskach zasilacza przy awarii w pętli sprzężenia zwrotnego oraz funkcja VCC clamp, zapobiegająca przekroczeniu na zaciskach sterownika dopuszczalnego napięcia, gdyby z jakichś powodów zasilacz się nie uruchomił.

Wydajność zintegrowanego tranzystora przełączającego jest wystarczająca do budowy zasilacza w topologii flyback o mocy wyjściowej do 10-12 watów przy zasilaniu z sieci 230 VAC oraz 6-7 watów dla jednostek akceptujących napięcie wejściowe zmieniające się w szerokim zakresie od 85 do 265 VAC.

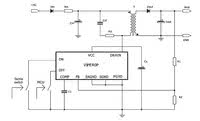

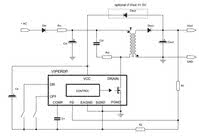

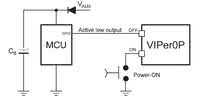

Na rysunku 1 pokazano schemat blokowy sterownika VIPer0P, a uproszczony schemat aplikacyjny przetwornicy zaporowej z VIPer0P na rysunku 2.

Zero-power

Tryb zero-power oznacza specjalny stan pracy jałowej układu VIPer0P, w którym układ jest zablokowany, przełączanie tranzystora MOSFET zostaje wstrzymane i do wyjścia nie jest kierowana energia zasilająca. Układ wchodzi w taki stan przez zwarcie z masą końcówki OFF i wychodzi z niego po zwarciu z masą końcówki ON.

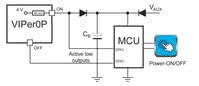

Przełączanie stanów może być dokonywane ręcznie za pomocą przycisków, linii mikrokontrolera (rys. 3) lub jako kombinacja tych metod, np. wyłączanie przez sygnał z mikrokontrolera, a wybudzanie za pomocą przycisku (rys. 4).

W układzie z rysunku 3 dodatkowo zapewnione jest zasilanie dla MCU za pomocą rezystora 45 kΩ zawartego w strukturze sterownika połączonego z zasilaczem wewnętrznym o napięciu 4 V (patrz rys. 1). Rezystancja ta została tak dobrana, aby utrzymać mikrokontroler w stanie czuwania i zasilania oraz pozwolić na wzbudzenie MCU i zasilacza bez zwiększania pobieranej mocy z sieci.

Innymi słowy tryb zero-power pozwala na konstrukcję zasilacza dla systemu mikrokontrolerowego, który można uśpić podobnie jak MCU i sprowadzić problem z mocą standby do zera.

Robert Magdziak