Przyczyną sprzeczności dużej szybkości z małą mocą zasilania pamięci SRAM jest technologia. W niskoprądowej SRAM jest stosowana specjalna technika sterowania GIDL (Gate-induced Drain Leakage), służąca do ograniczenia prądu spoczynkowego, a zatem i mocy zasilania. W tym celu w ścieżkach podciągających i ściągających stosowane są dodatkowe tranzystory, które zwiększają opóźnienie, a więc i czas dostępu.

W szybkich SRAM najważniejszy jest czas dostępu, dlatego technika ta nie może być stosowana. Rozmiary tranzystorów w celu skrócenia czasu propagacji zostały w nich zwiększone dla przyspieszenia przepływu ładunków, ale skutkuje to niestety zwiększeniem poboru prądu.

IoT wymaga oszczędności i wydajności

Przybywa obecnie aplikacji zasilanych bateryjnie i z bateryjnym podtrzymywaniem. Znaczna część nowych urządzeń - medycznych, przenośnych, konsumenckich, komunikacyjnych, przemysłowych - zaliczana jest do klasy IoT, co rewolucjonizuje sposoby ich funkcjonowania i komunikowania się. Wiele z istniejących komponentów nie spełnia wymagań tych urządzeń, bo potrzebuje dużej mocy zasilania.

A podzespoły oszczędne są zbyt powolne, aby spełniać wymagania bardziej złożonych aplikacji. Niezbędne są nowe podzespoły wysoko sprawne i zarazem energooszczędne. Dotyczy to zwłaszcza pamięci, ponieważ o szybkości systemu decyduje jego najpowolniejszy składnik, którym najczęściej jest pamięć zewnętrzna.

Potrzeba obniżenia mocy zasilania skupiła się początkowo na mikrokontrolerach, zmuszając producentów do szukania alternatywy dla tradycyjnych trybów ich działania: aktywnego i uśpionego. Firmy zaoferowały jednostki ze specjalnym trybem niskomocowym, zwanym trybem uśpienia głębokiego.

Kontrolery te normalnie działają z pełną szybkością, ale na czas, gdy ich praca nie jest niezbędna, mogą być bez jakiejkolwiek szkody wprowadzane w tryb głębokiego uśpienia, w którym pobór prądu spada do poziomu nanoamperów. Współczesne kontrolery mogą też działać z częstotliwością ponad 100 MHz, znacznie szybciej niż dotychczasowe, co również sprzyja oszczędności energii, gdyż zadania są wykonywane szybciej. Ale poza optymalizowaniem pracy kontrolera niezbędne jest jeszcze ograniczenie poboru prądu przez peryferia, a zwłaszcza pamięci.

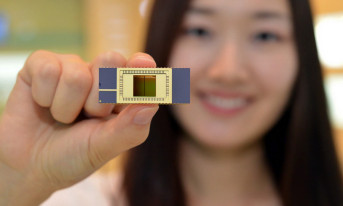

W rozmaitych systemach przenośnych oprogramowanie jest lokowane w pamięci Flash, ale do przechowywania danych inicjalizujących oraz wynikowych używana jest pamięć SRAM. W porównaniu do pamięci DRAM i Flash, pojemność SRAM jest ograniczona, aktualnie do około 8 MB, podczas gdy pojemność DRAM liczona jest w GB.

Jednakże DRAM czy Flash nie nadają się do bezpośredniej współpracy z mikrokontrolerem z powodu długiego czasu dostępu. Ponadto cykl odświeżania zawartości DRAM zwiększa jej energochłonność. Szybko działający mikrokontroler do przechowywania krytycznych danych i szybkiego wykonywania obliczeń potrzebuje pamięci cache. Do takiego zadania najlepiej nadaje się SRAM.

Pamięci SRAM dają się przełączać pomiędzy stanem aktywnym i uśpionym bez utraty danych i są zwykle podtrzymywane małą baterią guzikową. Dobrze spełniają się w roli zapewniania systemowi dużej szybkości cache w stanie aktywnym i małego poboru prądu w czasie uśpienia.

W razie zaniku zasilania w systemie SRAM jest przez układ zarządzania mocą PMIC przełączana na zasilanie bateryjne i unieruchamiana. System może pozostawać w takim stanie przez czas życia ogniwa.

Po ponownym włączeniu zasilania PMIC stopniowo przełącza SRAM na zasilanie systemowe, co zajmuje zwykle od 1 do 10 ms. Nie zakłóca to pracy systemu, ponieważ przechodzenie kontrolera do normalnej pracy również wymaga czasu.

Fast SRAM

Przez lata SRAM utrzymywała kompromisową pozycję szybko działającej i niskoprądowej hybrydowej pamięci SRAM, pod nazwą Fast SRAM. Jednak obecnie nie jest ona zdolna spełnić wszystkich oczekiwań. Teraz najlepszym rozwiązaniem jest SRAM zasilana on-chip w sposób podobny do sposobu zarządzania zasilaniem mikrokontrolera.

Oprócz aktywnego i spoczynkowego trybu działania obsługuje też tryb uśpienia głębokiego. Rozwiązanie to w trybie aktywnym umożliwia pełną szybkość dostępu do danych w SRAM, a w trybie uśpienia głębokiego blokuje wszelkie operacje pamięci, skrajnie ograniczając pobór prądu zasilania do natężenia około tysiąckrotnie mniejszego niż standardowe w trybie spoczynkowym Fast SRAM.

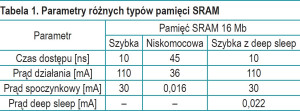

Tabela 1 przedstawia porównanie poboru prądu i czasu dostępu dla dwóch rodzajów SRAM, szybkiej i niskoprądowej, a także Fast SRAM z trybem uśpienia głębokiego. Liczby wyraźnie wykazują przewagę Fast SRAM z uśpieniem głębokim nad zwykłą Fast SRAM. Przewaga ta jest jeszcze większa w tych aplikacjach, w których SRAM przez większość czasu pozostaje w trybie spoczynkowym.

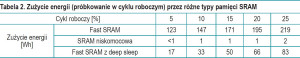

W bateryjnych systemach najnowszej generacji optymalne działanie pamięci jest osiągane przez zbalansowanie czasu potrzebnego na zapisanie danych z pobieranym w tym czasie prądem. Niech za przykład posłuży aplikacja, w której 100 kB danych musi zostać zapisane w ciągu 1 ms. W pamięci Fast SRAM zapisanie dwóch bajtów zabiera 10 ns.

Zatem pobór mocy wyniesie 130 Wh w ciągu 1000 godzin pracy. Natomiast zwykła energooszczędna SRAM zużyje w tym czasie tylko 2 Wh. To znacznie mniej, jednak trzeba też pamiętać o tym, że proces zapisu nie dotyczy tylko pamięci. SRAM nie jest jedynym czynnym komponentem w układzie w tym czasie.

Uwzględnienie w rachunku zużycia energii przez mikrokontroler poprawia trochę powyższe relacje, bo zapis do Fast SRAM jest znacznie szybszy, a więc trwa krócej. Niemniej dopiero użycie Fast SRAM z trybem głębokiego uśpienia jest w stanie zapewnić kompromis szybkości i energooszczędności.

Wyniki pomiarów pokazane w tabeli 2 pokazują, że skrócenie cyklu zapisu danych dzięki użyciu Fast SRAM z deep sleep przedłuża czas życia baterii o około 20% w porównaniu do użycia SRAM niskoprądowej.

|

Wszelkie działające systemy elektroniczne można podzielić na następujące kategorie:

|

Czasy usypiania i wybudzania

Istotnym parametrem działania mikrokontrolera czy pamięci są czasy potrzebne do ich wprowadzenia w tryb uśpienia i wybudzenia. Gdy są one długie, cały zysk z Fast SRAM z deep sleep może zostać zniweczony. Uzyskanie szybkiej i niskomocowej pamięci w IoT wymaga zatem dobrania mikrokontrolera i pamięci pod tym kątem.

W praktyce zachodzi też konieczność przeprojektowania systemu pod kątem wykorzystania trybu uśpienia głębokiego, co zwłaszcza w systemach z podtrzymaniem bateryjnym może być kłopotliwe.