Czym jest EOS?

EOS jest ogólnym terminem opisującym przeciążenie elektryczne na skutek przyłożenia do obwodu zbyt wysokiego napięcia. Niemniej ważne jest, aby pamiętać, że EOS jest funkcją mocy i czasu i tym samym skutki przeciążenia muszą być odnoszone do stopnia przeciążenia i czasu trwania.

EOS jest ogólnym terminem opisującym przeciążenie elektryczne na skutek przyłożenia do obwodu zbyt wysokiego napięcia. Niemniej ważne jest, aby pamiętać, że EOS jest funkcją mocy i czasu i tym samym skutki przeciążenia muszą być odnoszone do stopnia przeciążenia i czasu trwania.

Wyobraźmy sobie 1-omowy rezystor 1-watowy, na którym panuje 1,1-woltowe napięcie. Wówczas wydzielana moc cieplna wyniesie 1,21 W, gdyż jak wiadomo P=U²/R. Skoro rezystor ma dopuszczalną moc znamionową 1 W, napięcie to spowoduje jego przeciążenie. Niemniej wiadomo, że specyfikacje parametrów mają pewien margines zapasu, więc w praktyce nic się nie stanie przy takim małym przekroczeniu wydzielanej mocy ponad ten dopuszczalny 1 W.

Co będzie jednak, jeśli napięcie zwiększy się do 2 V? Wówczas moc cieplna sięgnie 4 W, co już jest sporym przeciążeniem, ale dalej, jeśli tylko czas będzie dostatecznie krótki, całość nie nagrzeje się tak bardzo, aby element ten uległ uszkodzeniu. A co, jeśli zwiększy się napięcie do 10 V, ale tylko na bardzo krótko, np. na 10 ms? Tu odpowiedź nie jest już prosta i nie ma sposobu, aby bez drobiazgowej analizy i pomiarów ocenić konsekwencje takiego przeciążenia.

Podatność elektroniki na przeciążenia elektryczne

Ogólnie rzecz biorąc, wszystko, co zawiera elektronikę, jest podatne na EOS. Części szczególnie wrażliwe to te, które łączą się ze światem zewnętrznym, jak porty USB czy obwody AFE (Analog Front End), ponieważ prawdopodobnie one są najczęściej narażone na wyładowania elektrostatyczne (ESD), uderzenia pioruna i tak dalej.

Ponieważ termin EOS jest pojęciem bardzo szerokim, grupa specjalistów z IEC i innych organizacji branżowych dokonała podziału tych zjawisk na odrębne kategorie, grupując w nich zdarzenia najczęściej spotykanie w rzeczywistości. Ten podział dostępny jest w ramach tzw. specyfikacji (norm) IEC.

Tabela 1 pokazuje trzy takie specyfikacje, które określają, jakie zdarzenia EOS można napotkać w projektowanym urządzeniu. W dalszym ciągu tego artykułu szczegółowo omówione zostaną tylko wyładowania ESD, niemniej warto pogłębić też wiedzę na temat szybkich transjentów (EFT) i przepięć.

Zagadnienia związane z wyładowaniami ESD są w projektach często ignorowane, bo inżynierowie wiedzą, że układy scalone mają wbudowane obwody ochronne i ktoś już o ochronie za nich pomyślał. To prawda, że takie zabezpieczenia są, niemniej ich przeznaczenie jest inne. Obwody ochronne w chipach są zaprojektowane do ich ochrony przed ESD podczas produkcji i transportu, a nie w sytuacjach, gdy komponenty te zostały użyte w systemach i są zasilane.

To rozróżnienie jest bardzo ważne, ponieważ gdy wzmacniacz jest zasilany, może zachowywać się zupełnie inaczej, gdy jest wystawiony na działanie elektryczności statycznej, niż gdyby nie był podłączony do niczego. Wyładowanie ESD w niezasilaną część może zostać rozproszone przez wewnętrzne diody zabezpieczające.

Z kolei, gdy trafiono w zasilaną część obwodu, może jednak spowodować, że wewnętrzne struktury chipu ulegną uszkodzeniu, bo będą musiały zmierzyć się z prądem normalnym i jeszcze tym pochodzącym z wyładowania. Na skutek tego skuteczna ochrona nie jest wcale łatwa, a na dodatek nie ma prostego rozwiązania wszystkich sytuacji.

Zdarzenia określające, czy element przetrwa przeciążenie wywołane przez EOS, można podzielić na dwie grupy. Pierwsza zawiera czynniki, nad którymi nie mamy kontroli, druga te, nad którymi można mieć kontrolę. Rzeczy, nad którymi projektant nie ma kontroli, to:

- kształt impulsu: ESD, EFT i udary mają bardzo różne charakterystyki,

- niektóre technologie półprzewodnikowe są bardziej podatne na wyładowania niż inne. Na przykład procesy CMOS są podatne na zatrzaśnięcie (latch-up),

- konstrukcja wewnętrznych obwodów ochronnych w chipach - jest tak wiele sposobów ich zaprojektowania, przez to schemat ochrony, który działa dla jednego, może nie działać dla innego. Niektóre rozwiązania mają wbudowane detektory, które włączają struktury zabezpieczające, jeśli wykryty zostanie wystarczająco szybki przebieg wyładowania na wejściu. Może to oznaczać, że układ, który normalnie przetrwa ESD, może ulec awarii, gdy konstruktor doda na wejściu typowy filtr RC. Jest to sprzeczne z intuicją, ale bardzo ważne jest, aby uświadomić sobie - popularna metoda ochrony przez filtr RC na wejściu - może pogorszyć problem.

Kolejna lista obejmuje to, nad czym projektant ma kontrolę:

- projekt PCB: im bliżej miejsca wyładowania znajdują się obwody, tym bardziej prawdopodobne jest, że dotrze do nich przebieg fali wyładowania o wyższej energii. Dzieje się tak dlatego, że energia wyładowania przemieszcza się "w dół" ścieżki i stopniowo rozprasza swoją energię na EMI i ciepło powstające na rezystancji ścieżek i propaguje na resztę obwodu na skutek pasożytniczych pojemnościowych i indukcyjnych sprzężeń z pobliskimi obwodami.

- obwody ochronne: gdy są dobrze zaprojektowane, są w stanie ochronić urządzenie, więc trzeba się starać je wykorzystywać.

Warto też dodać, że obwody zabezpieczające wejścia wzmacniaczy AFE przed nadmiernym stałym napięciem (over voltage protection - OVP) i potencjałami przekraczającymi napięcie zasilania (over the top - OTT) nie nadają się do ochrony przez wyładowaniami ESD.

Ich zadaniem jest generalnie ochrona przed prostymi pomyłkami i niewielkimi przekroczeniami, np. poprzez chwilowe podanie napięcia 12 V do wejścia 5 V na skutek użycia złego zasilacza, a nie przed impulsami na poziomie 8 kV!

Które zabezpieczenia będą skutecznie działać?

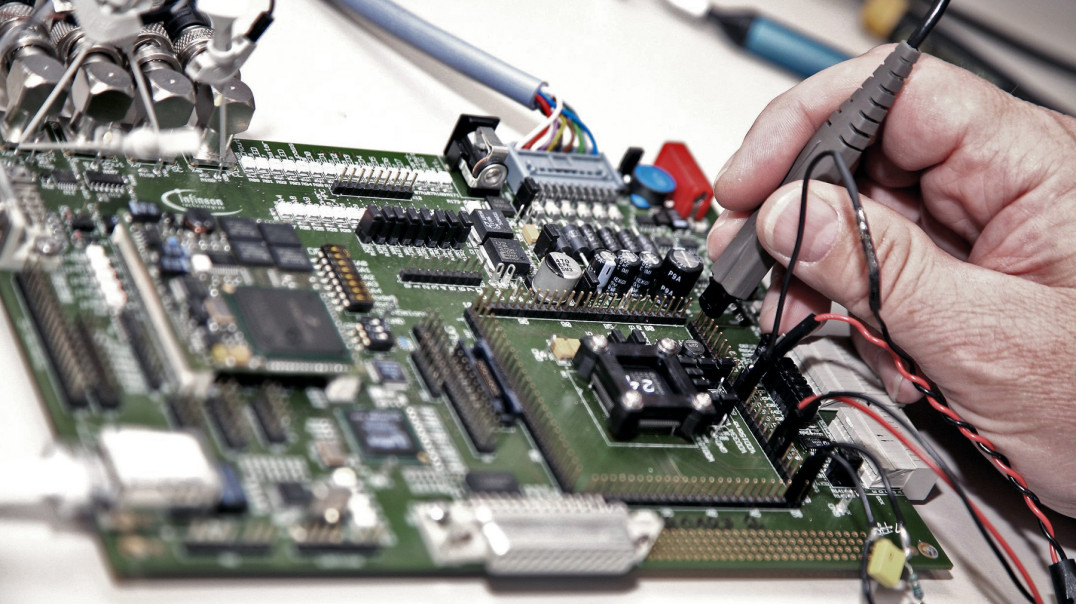

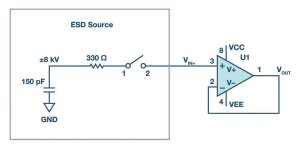

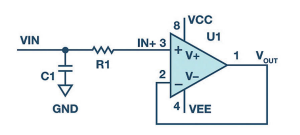

Istnieje wiele metod ochrony i jest mnóstwo podzespołów do tych celów. Podczas własnych badań w zakresie układów wejściowych AFE warto poddać analizie wzmacniacz operacyjny w konfiguracji bufora. Jest to najbardziej wrażliwy na przeciążenia przypadek, ponieważ wejście nieodwracające "widzi" cały impuls wyładowania i nie ma żadnych innych obwodów, gdzie jego energia mogłaby się chociaż częściowo rozproszyć (rys. 4).

R1 powinien być rezystorem wytrzymującym impulsy prądu o dużym natężeniu (typu thick film), a ponieważ jego szum jest proporcjonalny do pierwiastka kwadratowego z wartości rezystancji, jej wartość powinna być możliwie mała. C1 powinien być kondensatorem ceramicznym w obudowie nie mniejszej niż 0805, aby wyładowania nie mogły przeniknąć po jej powierzchni.

Pojemność ta powinna mieć współczynnik temperaturowy co najmniej klasy X5R (najlepiej C0G/NP0), aby utrzymać przewidywalne parametry ochrony w całym zakresie temperatur pracy. Możliwie niska indukcyjność szeregowa i rezystancja też są pożądane, aby kondensator mógł skutecznie absorbować wyładowania. Oczywiście powinien mieć także możliwie najwyższe napięcie znamionowe (minimum to 100 V).

C1 w tym przypadku znajduje się w układzie przed R1, ponieważ tworzy dzielnik pojemnościowy z kondensatorem 150 pF (z rys. 4) rozładowującym przebieg testowy ESD do badanego obwodu i przejmuje energię wyładowania, zanim wzmacniacz ją "zobaczy".

Chociaż taka metoda ochrony układów AFE nie jest popierana przez producentów kondensatorów, wykazano jej skuteczność w setkach testów. Oczywiście kluczowe z punktu widzenia skuteczności ochrony są tutaj parametry kondensatora.

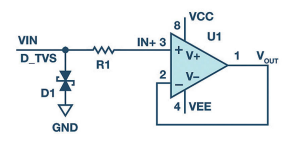

Zamiast pojemności - dioda TVS

W przypadku, gdy do ochrony wykorzystamy diodę TVS (Transient Voltage Supressor), podobnie jak w przypadku sieci RC, rezystor R1 powinien mieć zdolność wytrzymania impulsów prądu o dużym natężeniu. Tu też może on wprowadzać do układu niepożądany szum. Typ diody D1 należy określić dla norm IEC, które muszą być przestrzegane.

Niektóre mogą obejmować tylko ESD, ale inne aplikacje wymuszają też ochronę przed EFT i udarami. Dioda powinna być dwukierunkowa, aby mogła tłumić zarówno dodatnie, jak i ujemne impulsy. Jej napięcie blokowania (aktywacja działania) musi zostać dobrana tak, aby było ono możliwie jak najwyższe.

Zbyt niskie może wywołać upływność podczas normalnej pracy, a z kolei zbyt wysokie spowodować, że ochrona nie zadziała. Wiele osób uważa, że diody TVS mają za duży prąd upływu dla współczesnych układów analogowych i dlatego nie mogą być używane w precyzyjnych układach AFE, np. w aparaturze pomiarowej. To niekoniecznie prawda.

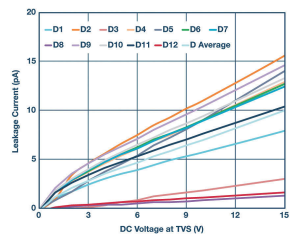

Wiele kart katalogowych pokazuje, że prąd upływu jest wysoki, nawet sięga 100 μA, ale faktem jest, że płynie on tylko przy maksymalnym napięciu roboczym i w maksymalnej temperaturze rzędu 150°C. Co więcej, wszystkie TVS-y mają duży prąd upływu powyżej 85°C, ale w typowych temperaturach otoczenia prądy te są znacznie mniejsze. Rysunek 7 przedstawia dane zebrane podczas pomiaru upływności 12 takich samych diod TVS.

Najgorsza miała upływność tylko 7 pA przy 5 V. To ponad 10 mln razy lepiej niż w najgorszym przypadku wymienionym w karcie katalogowej. Oznacza to, że jeśli tworzony system nie doświadczy temperatury wyższej niż 85°C, diody TVS mogą być dobrym rozwiązaniem ochronnym.

Wyniki testów

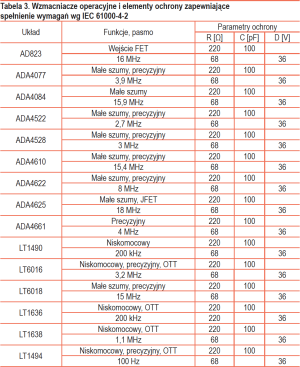

Tabela 3 pokazuje wyniki testów szeregu wzmacniaczy operacyjnych zgodnie ze standardami IEC ESD. Mimo że standard ESD przewiduje test trzech wyładowań przy ±8 kV, wszystkie badane obwody ochronne przeszły pomyślnie test 100 impulsów przy ±9 kV i zapewniają tym samym wystarczający margines ochrony.

Normy IEC wymagają podłączenia uziemienia źródła impulsów ESD do masy wzmacniacza za pomocą dwóch rezystorów 470 kΩ równolegle z pojemnością 30 pF. Ta konfiguracja testowa była bardziej wymagająca, ale nadal ochrona była skuteczna.

Do testów wykorzystano rezystory firmy Panasonic 0805 ERJ-P6, kondensatory Yageo 0805 100 V C0G/NPO, diody TVS: Bourns CDSOD323-T36SC (dwukierunkowa, 36 V, niski prąd upływu), a także warystory Bourns MLA, 0603 26 V.

Warystory ESD pojawiły się w teście nieprzypadkowo. Diody TVS działają świetnie i mogą dowolną liczbę razy tłumić wyładowania. Jest to niezbędne w przypadku ochrony przed EFT i udarami, ale jeśli wszystko, czego potrzeba, to ochrona ESD, warystory ESD mogą być niezłą alternatywą. Są to rezystory o bardzo wysokiej wartości. Gdy napięcie na ich zaciskach przekroczy próg aktywacji, ich rezystancja skokowo maleje do niskiej wartości. Dzięki temu warystor pochłania energię, zamieniając ją na ciepło.

Są one implementowane tak samo jak diody TVS, ale w odróżnieniu od diod mają mały prąd upływu oraz kosztują mniej niż połowę tego co TVS-y. Wadą jest to, że ich skuteczność maleje z każdym wyładowaniem. Warystory ESD były również testowane w układach wymienionych w tabeli 3 i działały najlepiej, gdy rezystor szeregowy był około dwukrotnie większy niż dla diody TVS.

Co z EFT i udarami?

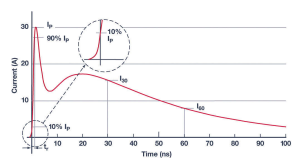

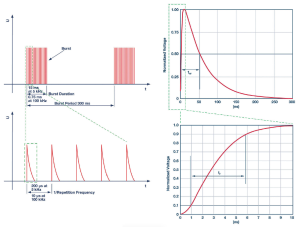

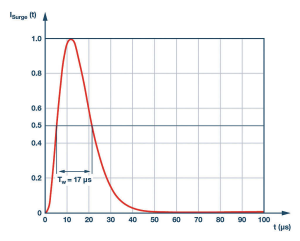

Wzmacniacze z tabeli 3 zostały przetestowane tylko pod kątem ochrony przed ESD. Test EFT jest od niego odmienny, ponieważ impulsy pojawiają się w seriach (5 kHz lub więcej) i mają wolniejszy czas narastania (5 ns), chociaż napięcie nie jest tak wysokie (4 kV i niższe). Z kolei test udarowy (Surge) jest około 1000 razy silniejszy niż EFT, ale jest jednocześnie bardzo krótki. Jeśli konieczne jest również zapewnienie ochrony wg tych standardów, trzeba się upewnić, że elementy ochronne wytrzymają takie przeciążenia.

Podsumowanie

Filtr RC lub dioda TVS wydają się prostymi elementami ochronnymi i łatwymi w integracji, niemniej przy ich użyciu należy pamiętać o wszystkich innych zagadnieniach wymienionych w tym artykule, które wpływają na wydajność i parametry aplikacji i stopień ochrony obwodów AFE.

Arrow Electronics Poland