Do syntezy częstotliwości w zakresie do ok. 30 GHz nadają się analogowe syntezery bazujące na pętli synchronizacji fazy (PLL). Jeszcze lepsze właściwości mają syntezery typu Integer N, które mnożą częstotliwość odniesienia przez liczbę całkowitą i wersje ułamkowe N, które mnożą częstotliwość odniesienia przez niecałkowite wartości ułamkowe. Takie układy wykorzystują specjalne techniki, które minimalizują szum fazowy i eliminują inne niedoskonałości. W tym artykule opisano konstrukcję syntezerów o częstotliwości całkowitej i ułamkowej N w oparciu o przykładowe rozwiązania z oferty firmy Analog Devices.

Syntezatory z zamkniętą pętlą fazową typu Integer N

Pętle PLL są używane do kontroli częstotliwości i fazy sygnału w układach generatorów zegarowych, mnożników częstotliwości, w demodulatorach, generatorach śledzących lub w obwodach odzyskiwania sygnału zegarowego przy transmisji asynchronicznej. Każda z takich aplikacji wymaga innej charakterystyki działania układu PLL, ale wszystkie wykorzystują tę samą podstawową koncepcję działania.

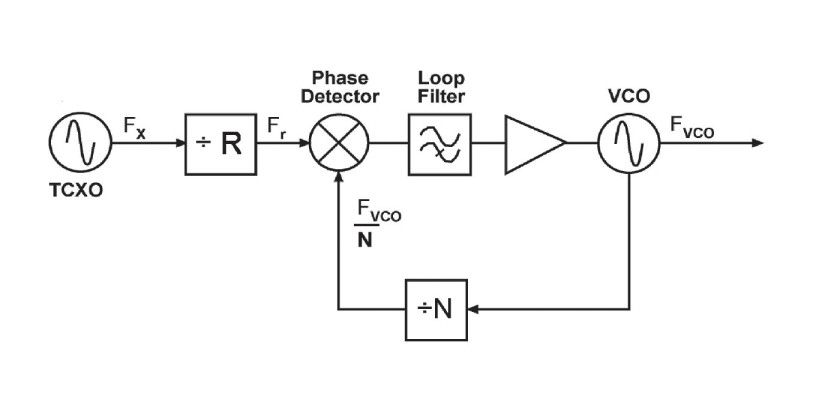

Rysunek 1 przedstawia schemat blokowy podstawowej wersji pętli PLL skonfigurowanej jako mnożnik częstotliwości.

Działanie tego obwodu jest typowe dla wszystkich pętli synchronizacji fazowej. Jest to w zasadzie układ sterowania ze sprzężeniem zwrotnym, który reguluje fazę oscylatora przestrajanego napięciem (VCO). Sygnał wejściowy jest podawany do preskalera, który dzieli częstotliwość wejściową przez współczynnik R. Na jego wyjściu dostępna jest częstotliwość odniesienia, która podawana jest dalej na jedno wejście detektora (komparatora) częstotliwościowo-fazowego (PFD).

Na drugie wejście PFD podawany jest sygnał sprzężenia zwrotnego z wyjścia licznika dzielącego przez N. Zwykle, jeśli PLL jest zablokowany (zsynchronizowany), częstotliwości obu sygnałów będą prawie takie same. Sygnał wyjściowy detektora fazy jest napięciem proporcjonalnym do różnicy faz sygnałów między dwoma wejściami. Jeśli pętla jest odblokowana (niezsynchronizowana), jak ma to miejsce podczas uruchamiania lub jeśli występuje duże chwilowe przesunięcie częstotliwości na wejściu (np. podczas przełączania kanału), wówczas detektor reguluje częstotliwość generatora VCO do momentu ustawienia żądanej wartości. Po osiągnięciu tej częstotliwości PFD powraca do trybu detektora fazy i ma sygnał wyjściowy proporcjonalny do różnicy faz między częstotliwością odniesienia a sygnałem sprzężenia zwrotnego.

Detektor fazowo-częstotliwościowy steruje pompą ładunku, która jest bipolarnym przełączanym źródłem. Oznacza to, że może ona tworzyć dodatnie i ujemne impulsy prądu i podawać je do filtra pętli PLL, który wygładza sygnał błędu fazy, a także określa odpowiedź dynamiczną PLL (np. szybkość regulacji). Przefiltrowany sygnał reguluje częstotliwością VCO. Należy zauważyć, że sygnał wyjściowy VCO ma częstotliwość, która jest N-krotnością sygnału wejściowego dostarczanego na wejście odniesienia częstotliwości do detektora częstotliwości fazowej i jest równa N/R krotności częstotliwości wejściowej. Ten sygnał wyjściowy jest przesyłany z powrotem do detektora fazy poprzez dzielenie przez N w liczniku.

Zwykle filtr pętli projektowany jest tak, aby jego charakterystyka pasowała do wymagań aplikacyjnych pętli PLL. Jeśli PLL ma śledzić sygnał, szerokość pasma filtru będzie większa niż w przypadku, gdyby chodziło o ustalenie stałej częstotliwości. Zakres częstotliwości, dla których PLL jest w stanie się zsynchronizować, nazywany jest "zakresem przechwytywania". Po zablokowaniu pętli i przy śledzeniu sygnału zakres częstotliwości, w ramach którego będzie podążać PLL, nazywany jest "zakresem śledzenia". Ogólnie zasięg śledzenia jest większy niż zasięg przechwytywania. Filtr pętli PLL określa również, jak szybko może zmieniać się częstotliwość sygnału, aby synchronizacja nie została zerwana – tj. maksymalną szybkość zmian.

Im węższa szerokość pasma filtru pętli, tym mniejszy błąd fazy w stanie synchronizmu. Dzieje się to kosztem wolniejszej odpowiedzi pętli i zmniejszonego zasięgu przechwytywania. Takie właściwości mają układy PLL używane w aplikacjach zegarowych, bo działają głównie na stałych częstotliwościach. Ogólnie szerokość pasma filtra pętli powinna być znacznie mniejsza niż częstotliwość odniesienia.

Ponieważ częstotliwość wyjściowa PLL jest całkowitą wielokrotnością częstotliwości odniesienia (referencyjnej, często jest to tzw. skok międzykanałowy), rozdzielczość częstotliwości jest równa częstotliwości odniesienia. Uzyskanie dokładniejszej rozdzielczości częstotliwości wymaga jej zmniejszenia, czego dokonuje się za pomocą preskalera R.

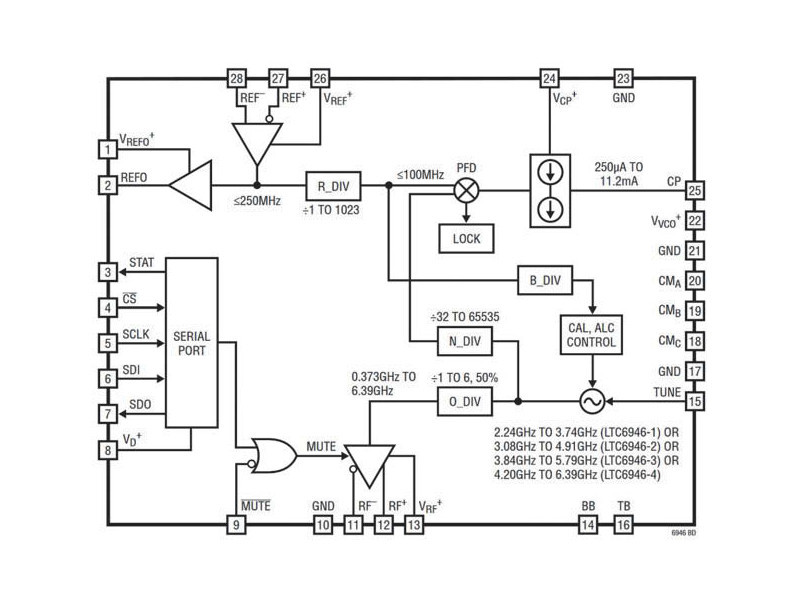

Przykładem pętli PLL typu Integer N jest LTC6946 firmy Analog Devices. Jest to niskoszumowy syntezer o częstotliwości od 0,64 do 5,79 GHz ze zintegrowanym VCO i doskonałą czystością tworzonego sygnału (rys. 2). Układ jest członkiem rodziny czterech produktów tego typu, każdy z tych elementów ma inny zakres częstotliwości od 0,373 do 6,39 GHz.

Układ wymaga zewnętrznego filtru pętli, który można zoptymalizować pod kątem określonej aplikacji. Ma też wewnętrzny preskaler o podziale od 1 do 1023. Dzielnik pętli ma zakres od 32 do 65535. Prąd pompy ładunkowej można regulować w zakresie od 250 μA do 11,2 mA w celu dopasowania do impedancji filtru PLL.

Syntezatory z ułamkową pętlą fazową

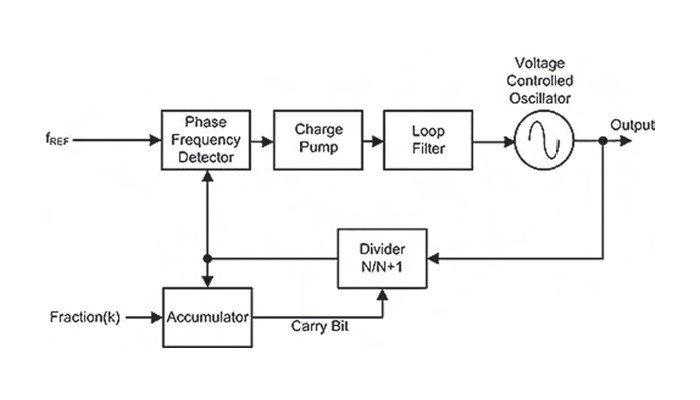

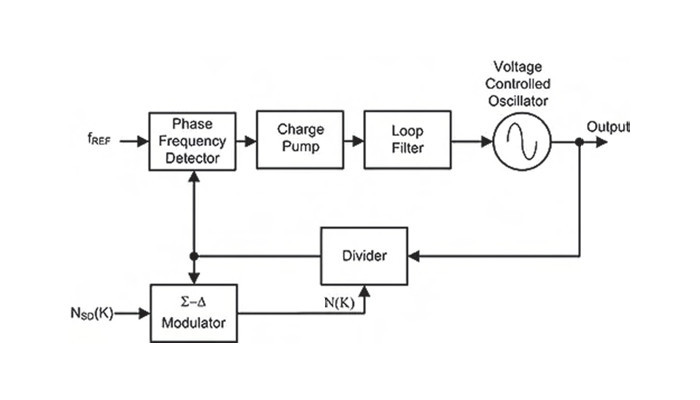

Rozdzielczość częstotliwości syntezera PLL można poprawić, zmniejszając rozmiar kroku do wartości mniejszych niż wartości całkowite, tj. realizując ułamkowe kroki w dzielniku pętli N. Osiąga się to poprzez dynamiczne zmienianie lub dithering wartości podziału. Oznacza to, że ustawienie dzielnika utrzymuje wartość N przez ustaloną liczbę cykli częstotliwości wyjściowej PLL i jest okresowo zwiększane do innej wartości, takiej jak N+1. Na przykład, jeśli ustawienie dzielnika wynosi 4 dla trzech okresów odniesienia i 5 dla czwartego cyklu odniesienia, to efektywny stopień podziału wynosi 4,25. Jednym ze sposobów osiągnięcia tego jest użycie akumulatora, jak pokazano na rysunku 3.

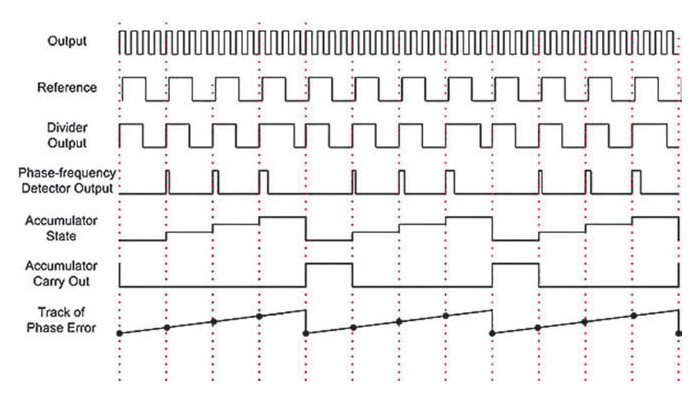

Akumulator zlicza impulsy wyjściowe z dzielnika, a każde M, gdzie M to modulo akumulatora, wysyła bit przeniesienia, który zmienia stan podziału na N+1. Rysunek 4 ilustruje przykład ustawienia dzielnika na 4,25.

Akumulator jest sterowany z podzielonego wyjścia i liczy modulo cztery, czyli M jest równe cztery. Co czwarty impuls generuje przeniesienie, które zwiększa podział o jeden. Akumulator kasuje się i zaczyna ponownie liczyć. Zwiększenie ustawienia podziału powoduje przesunięcie częstotliwości wyjściowej, co powoduje skumulowany błąd przesunięcia fazy. Wykres pokazuje wartość fazy w funkcji czasu (równoważny błędowi fazy).

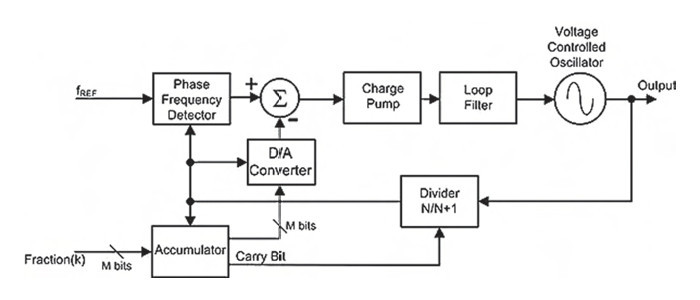

Średnie ustawienie dzielnika wynosi 4,25, ale wyjście syntezatora jest modulowane fazowo, co powoduje powstanie niepożądanych sygnałów w sygnale wyjściowym. Patrząc na stan akumulatora, widzimy, że śledzi on błąd fazy. Można to wykorzystać do usunięcia tych niepożądanych efektów, jak pokazano na rysuku 5.

Stan akumulatora jest konwertowany na sygnał analogowy przez przetwornik cyfrowo-analogowy (DAC), skalowany i odejmowany od sygnału wyjściowego detektora fazowo-częstotliwościowego w celu usunięcia modulacji fazy z powodu ułamkowego stopnia podziału N i wynikającego z niej ditheringu. Operacja ta musi być precyzyjna – jeśli sygnał korekcyjny nie pasuje dokładnie do błędu fazy, na wyjściu pojawią się niepożądane składowe.

Modulator sigma-delta

Okresowość podziału wywoływana przez akumulator jest przyczyną zniekształceń tj. pojawienia się niepożądanych sygnałów na wyjściu. Jeśli akumulator zostanie zastąpiony modulatorem sigma-delta, wówczas można zastosować techniki cyfrowe do modulacji stopnia podziału dzielników w sposób minimalizujący zniekształcenia. Ta zmiana jest pokazana na rysunku 6.

Realizacja modulacji sigma-delta opiera się głownie na dwóch technikach. Pierwsza polega na zwiększeniu liczby zliczeń dzielnika N w szerszym zakresie wartości, tak że średni współczynnik podziału da pożądaną wartość ułamkową dzielnika. Zmniejsza to zakres zmian. Syntezer oparty na akumulatorze zmienia liczbę między dwoma stanami. Jest to metoda modulacji pierwszego rzędu. PLL n-tego rzędu sigma-delta ułamkowa moduluje licznik N między 2n wartościami. Na przykład modulator trzeciego rzędu będzie przełączał się między ośmioma różnymi wartościami dzielnika, a modulator czwartego rzędu zmieniałby się między 16 różnymi wartościami dzielnika.

Druga technika nazywana jest ditheringiem – polega na randomizacji sekwencji 2N tak, aby była ona pseudolosowa. Utrzymując średni ułamkowy współczynnik dzielnika, można skonwertować składowe widma pochodzące od ułamkowego podziału na pseudolosowy szum w taki sposób, że może być filtrowany przez PLL.

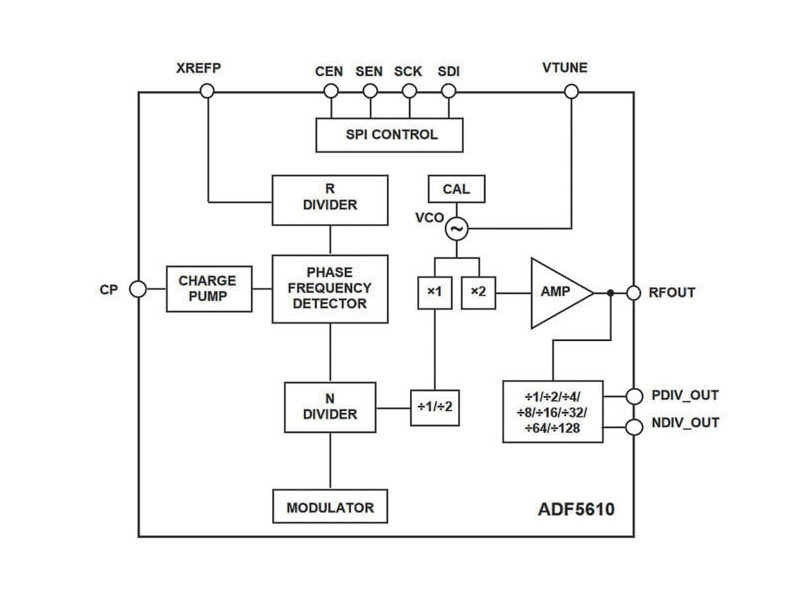

Taką wersją syntezera ułamkowego sigma-delta jest Analog Devices ADF- 5610. Jest to niskoszumowe rozwiązanie pracujące w zakresie częstotliwości od 0,57 MHz do 14,6 GHz ze zintegrowanym VCO (rys. 7).

ADF5610 wymaga zewnętrznego oscylatora odniesienia i filtra pętli. Ma zintegrowane VCO o częstotliwości podstawowej od 3650 MHz do 7300 MHz. Częstotliwości te są wewnętrznie podwajane i kierowane do pinu RFOUT. Jest też wyjście różnicowe, które pozwala na podzielenie podwojonej częstotliwości VCO przez współczynniki 1, 2, 4, 8, 16, 32, 64 lub 128, co pozwala na generowanie częstotliwości wyjściowych już od 57 MHz.

ADF5610 wykorzystuje zaawansowany modulator sigma-delta z 24-bitowym ułamkowym dzielnikiem, który zapewnia wyjątkowo mały poziom sygnałów niepożądanych. Podobnie jak we wszystkich syntezerach tego typu, układ ten wykorzystuje techniki cyfrowego przetwarzania sygnału, aby znaleźć pożądany średni ułamkowy współczynnik podziału. Proces ten taktowany jest z częstotliwością PFD i wytwarza pseudoszum modulacji wyjściowej zwany szumem kwantyzacji. Zewnętrzny dolnoprzepustowy filtr pętli pozwala na jego wyfiltrowanie do poziomu poniżej szumu fazowego VCO, zapobiegając w ten sposób ogólnemu wzrostowi szumu fazowego całej pętli.

ADF5610 realizuje również tryb generowania dokładnej częstotliwości z błędem 0 Hz. Umożliwia generowanie dokładnie ustalonej częstotliwości między sąsiednimi całkowitymi N krokami granicznymi podziału i wykorzystuje 24-bitowe modulo podziału w akumulatorze fazowym.

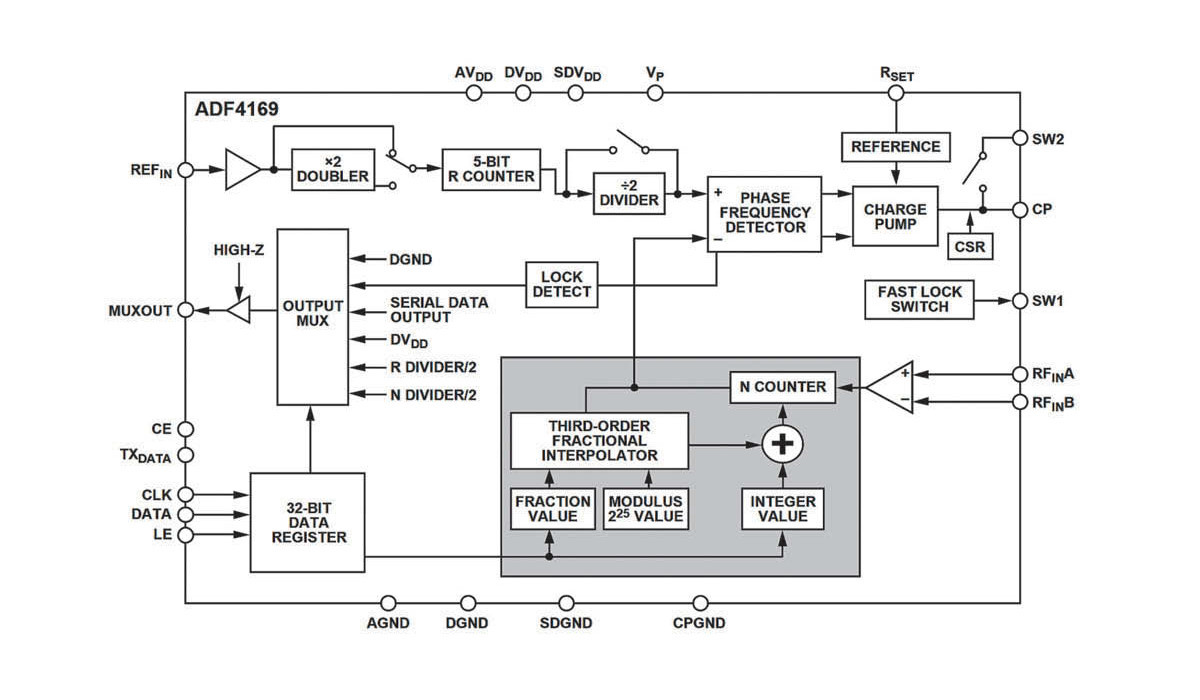

ADF4169 to kolejny syntezer PLL, który można skonfigurować z podziałem całkowitym lub ułamkowym. Działa w paśmie do 13,5 GHz i wykorzystuje zewnętrzne wejście częstotliwości odniesienia, generator VCO i filtr pętli. Zawiera modulator sigma-delta trzeciego rzędu do ułamkowej syntezy N, który można wyłączyć, umożliwiając pracę urządzenia w trybie całkowitoliczbowym (rys. 8).

Jeszcze innych syntezer ADF4158 jest przeznaczony do użytku w radarach z modulowaną częstotliwością i emisją CW (FMCW). Jest w stanie generować różne typy modulowanych przebiegów w dziedzinie częstotliwości, w tym piłokształtne i trójkątne. Jest to specjalna funkcja, która jest niezbędna w zastosowaniach radarowych.

Podsumowanie

Rosnące szybkości transmisji danych w szybkich magistralach komunikacji szeregowej wymagają od projektantów spojrzenia na nowe rozwiązania syntezerów PLL. Wersje wykorzystujące topologie z całkowitym i ułamkowym podziałem zapewniają stabilne sygnały o niskim poziomie szumów, umożliwiając budowę zegarów o wysokiej częstotliwości do układów komunikacji szeregowej i aplikacji radarowych dla częstotliwości do dziesiątek gigaherców.

Rolf Horn, Digi-Key Electronics

Digi-Key Electronics

https://www.digikey.pl/