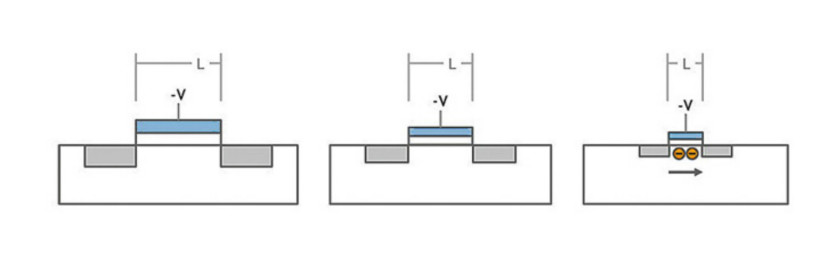

Tranzystory to w uproszczeniu przełączniki między dwoma stanami: włączonym oraz wyłączonym. W tranzystorach FET przewodność kanału kontroluje się za pomocą pola elektrycznego – przepływ elektronów pomiędzy źródłem a drenem zależy od napięcia przyłożonego do bramki. W przypadku tranzystorów z kanałem typu n elektrony przepływają od źródła do drenu po przyłożeniu do bramki napięcia dodatniego. Jeżeli z kolei napięcie bramka- źródło jest bliskie zera, przepływ prądu przez kanał jest zablokowany.

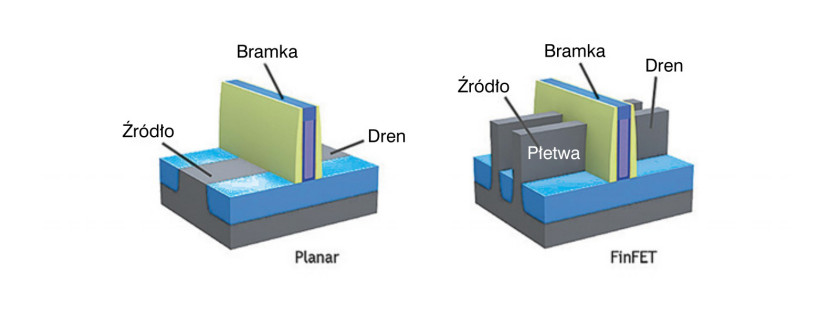

Technologia planarna

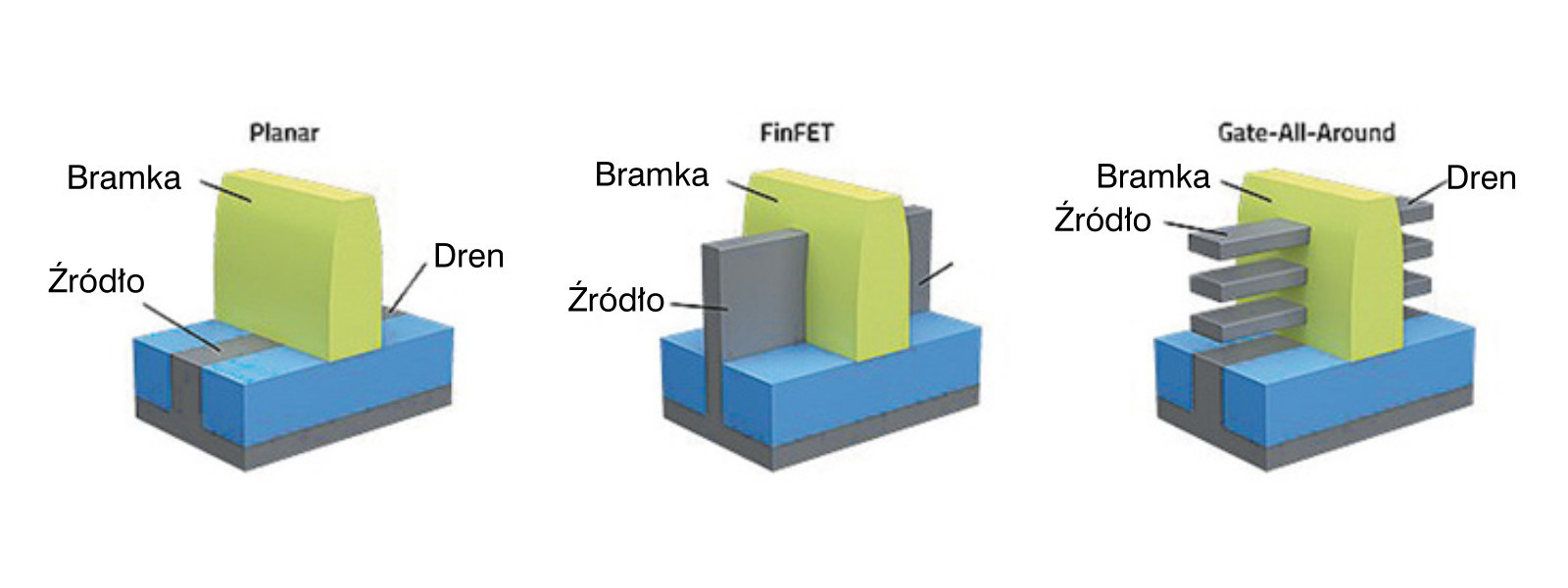

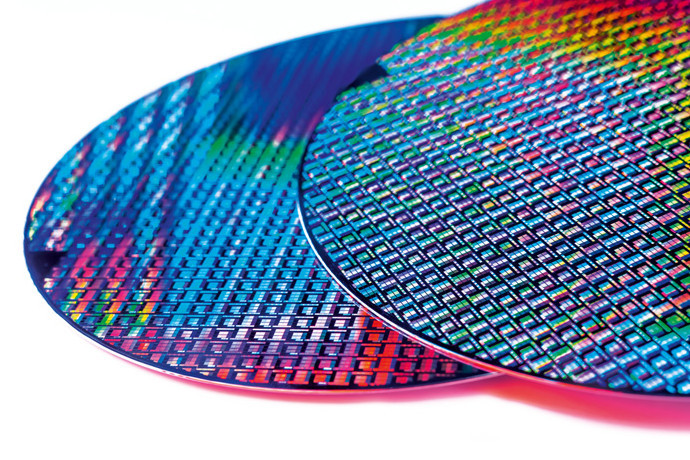

Tradycyjnie tranzystory FET wykonywane były w technologii planarnej, w której na krzemowym podłożu osadzano dielektryk (dwutlenek krzemu), stanowiący materiał bramki, a na nim warstwę przewodzącą elektrod bramki. Następnie na taką płytkę w procesie litografii nanoszony był wzór odwzorowujący rozkład struktur scalonych. W kolejnym kroku zgodnie z nim konkretne obszary płytki były wytrawiane, odsłaniając źródła oraz dreny. Miejsca te były następnie domieszkowane. Technologię planarną opracowano 60 lat temu, ale tranzystory wciąż są w ten sposób wykonywane. Niestety problemem w jej przypadku okazało się skalowanie. W końcu bowiem osiągnięto limit – około 20 nm, przy którym dalsze zmniejszanie długości bramki okazało się już niemożliwe. Wynikało to z niekorzystnych dla działania tranzystora efektów jak ten krótkokanałowy, w którym między źródłem a drenem mimo stanu wyłączenia płynie za duży prąd upływu. To nie pozwala na całkowite wyłączenie tranzystora. Ponadto przy tak małych geometriach na tranzystor przypadało tylko kilka atomów domieszek, więc każda brakująca lub dodatkowa cząstka miała znaczenie. Skutkiem różnic w poziomie domieszek w obrębie całej struktury scalonej były rozbieżności w długościach bramek. To natomiast powodowało różnice w napięciach progowych poszczególnych tranzystorów. Konsekwencją była konieczność zwiększenia napięcia zasilania w celu zapewnienia marginesu, który kompensowałby różnice napięć przełączania. To niestety zwiększało zużycie energii. Problemy te w końcu wymusiły intensyfikację prac nad alternatywnymi technologiami produkcji tranzystorów.

Technologia FinFET

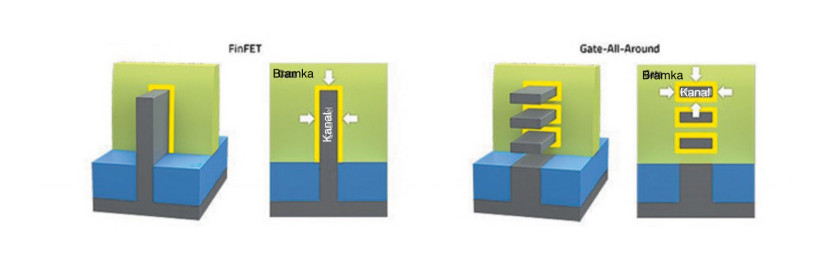

tranzystorze, nawet przy dalszym zmniejszaniu rozmiarów struktur scalonych, pozwoliło odzyskać podniesienie kanału ponad płaszczyznę płytki. W taki sposób powstała płetwa, która stała się charakterystycznym elementem konstrukcji FinFET. Dzięki temu bramka ma kontakt z kanałem z trzech stron, a nie tylko w poprzek jego górnej części. Większa powierzchnia styku zwiększa kontrolę nad polem elektrycznym, które także w tym przypadku wnika w kanał głębiej. W rezultacie efektywniej można regulować płynący nim prąd, ograniczając jego upływ w stanie wyłączenia. Kolejną zaletą jest mniejsze napięcie bramki, co ogranicza zużycie energii.

Chociaż ideę konstrukcji FinFET przedstawiono w 1999 roku, na jej komercjalizację trzeba było czekać aż do 2011 roku. Wówczas Intel, jako pierwszy, poinformował o wyprodukowaniu układów w technologii FinFET 22 nm. Firma zaprezentowała tranzystory w tej wersji pod własną nazwą Tri-Gate – w tej technologii wykonano Ivy Bridge, 22-nanometrową wersję procesora Sandy Bridge ×86. Rok później sporo zamieszania wywołała informacja o planach Achronix i Altery, które ogłosiły, że będą wykorzystywać technologię Intel Tri-Gate 22 nm do produkcji układów FPGA nowej generacji. Ostatecznie jednak, gdy wreszcie pojawiły się FPGA Altery oparte na FinFET Stratix 10, zostały one wykonane w już nowszej, 14-nanometrowej technologii Tri-Gate. Świadczyło to o tym, jak trudne oraz czasochłonne jest wdrożenie nowego podejścia w konstrukcji tranzystorów.

Pomimo to w tamtych czasach technologia FinFET została okrzyknięta najbardziej rewolucyjną zmianą, jakiej przemysł półprzewodnikowy doświadczył od ponad 50 lat, utorowała bowiem drogę dla skalowania 3D. Budując tranzystory w pionie, można dalej zmniejszać ich wymiary oraz upakować ich więcej na jednostce powierzchni układu scalonego. Nie oznacza to jednak, że w produkcji w technologii FinFET nie pojawiają się też nowe wyzwania.

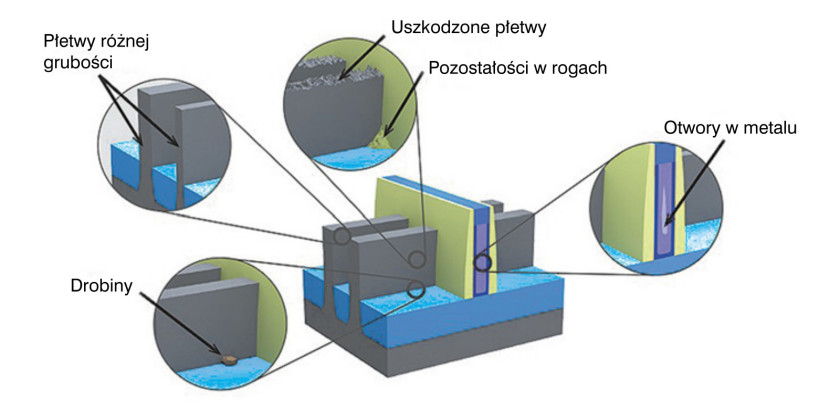

Przykładowo płetwy wykonywane są w ramach procesów SADP (Self-Aligned Double Patterning) i SAQP (Self-Aligned Quadruple Patterning). Wykorzystuje się w nich przekładki osadzane na ściankach bocznych struktury, które następnie są usuwane przez trawienie, pozostawiając płetwy. Ich wysokość i szerokość muszą być ściśle kontrolowane. Wymagana jest także selektywność trawienia, konieczna do usunięcia resztek z narożników płetwy i bramki, bez uszkadzania odsłoniętych powierzchni. Cienkie, delikatne struktury żeber i bramek są też wyzwaniem dla procesów czyszczenia. Problemy pojawiają się ponadto na etapie wypełniania bramki materiałem przewodzącym. Im struktura ta staje się węższa, tym trudniejsze staje się jego osadzenie bez wytworzenia się w środku otworu.

Przez ostatnich kilkanaście lat wyzwaniom tym udawało się jednak z powodzeniem sprostać. Dzięki temu konstrukcje FinFET przyczyniły się do tego, że prawo Moore'a wciąż obowiązuje. Niestety w końcu i one osiągnęły kres swojej użyteczności, przy około 7 nm.

Technologia GAAFET

Najnowszym rozwiązaniem w zakresie produkcji tranzystorów jest technologia GAAFET (Gate-All-Around FET). Zasadnicza modyfikacja w porównaniu do konstrukcji FinFET polega w jej przypadku na tym, że bramka będzie się stykać z kanałem nie tylko z trzech, ale ze wszystkich stron.

Proponowanych jest kilka wariantów technologii GAAFET. W wersji podstawowej będą wykorzystywane oddzielne poziome nanoarkusze ułożone warstwowo i otoczone ze wszystkich stron materiałem bramki. Taka konstrukcja zapewni lepszą kontrolę nad charakterystyką kanału w porównaniu do technologii FinFET.

W przeciwieństwie do tranzystorów w tej wersji, w których większy prąd wymaga większej liczby płetw umieszczonych obok siebie, obciążalność prądową tranzystorów GAA można zwiększyć przez ułożenie kilku nanoarkuszy pionowo, z materiałem bramki owiniętym wokół kanałów. To zapewnia znaczną oszczędność miejsca. Poza tym wymiary nanoarkuszy można skalować, dzięki czemu można dopasować rozmiar tranzystorów do określonej wydajności. Prognozuje się, że tak jak w przypadku płetw w tranzystorach FinFET, także szerokość i odstępy między arkuszami w GAAFET będą wraz z postępem miniaturyzacji maleć. W efekcie w końcu szerokość arkusza będzie mniej więcej taka sama jak jego grubość – wówczas będą to już nanodruty.

Obecnie w zakresie tytułowej technologii przoduje firma Samsung, która opracowała oraz opatentowała własną wersję tranzystorów GAA – Multi-Bridge Channel FET (MBCFET) z nanoarkuszami. W porównaniu z tranzystorami w technologii 5 nm te pierwszej generacji MBCFET 3 nm (3GAE, 3 nm Gate-All-Around) zapewniają zmniejszenie zużycia energii nawet o 45%, poprawę wydajności o 23% i zmniejszenie powierzchni na tranzystor o 16%. Oczekuje się, że kolejna generacja zapewni dalszą poprawę tych parametrów, ze zużyciem energii mniejszym o 50%, wydajnością lepszą o 30% i powierzchnią mniejszą o 35%. Samsung zapowiedział już wykorzystanie układów scalonych w tej technologii w szerokiej gamie urządzeń mobilnych, na potrzeby motoryzacji, sztucznej inteligencji oraz Internetu Rzeczy.

W tyle nie pozostają także inni czołowi producenci. Na przykład TSMC uruchomi produkcję w technologii GAAFET 2 nm do 2023 roku, natomiast Intel zaplanował start produkcji w technologii GAAFET pod własną nazwą RibbonFET 20A (20 angstremów) w 2024 roku.

Monika Jaworowska