Jednym z zagadnień związanym z przetwarzaniem i przechowywaniem danych jest problem mocy elektrycznej układów lub urządzeń realizujących ten proces. Niestety, oczywistość jest bardzo brutalna, zaskoczeń tu nie ma – wraz ze wzrostem ilości danych musi rosnąć moc elektryczna procesorów i innych elementów elektronicznych używanych w procesie przetwarzania danych. Następstwem tej zależności jest zwiększanie ciepła wydzielanego przez te układy i konieczność jej odprowadzania. Problemy związane z zasilaniem, w szczególności z ciepłem, dominują obecnie w pracach projektowych nad chipami i strukturami półprzewodnikowymi. Jak na razie wieści nie są dobre, problemy te stale poszerzają się i mnożą.

Gęstość tranzystorów w chipie osiągnęła punkt, w którym pracując jako maleńkie przełączniki cyfrowe, wytwarzają więcej ciepła, niż można usunąć dostępnymi dziś tradycyjnymi środkami. Rozwiązanie tego problemu wymaga zaangażowania całej branży obejmującej producentów struktur, dostawców materiałów, grup badawczych, działów analiz itp. Niestety, bardzo często opanowanie jednego zagadnienia generuje cały szereg nowych problemów.

U podstaw wszystkich działań leży ciągłe skupianie się na upakowywaniu coraz większej liczby tranzystorów na określonej powierzchni i związana z tym stale przyspieszająca walka z mocą strat. W tranzystorach FinFET zostały rozwiązane problemy z nieszczelną bramką w technologii 16/14 nm, ale kolejny problem pojawił się ponownie zaledwie dwa węzły dalej. W przypadku technologii 3 nm wprowadzono zupełnie inną strukturę tranzystorów GAAFET (Gate All Arounded FET, zwanych także nanosheets), stanowiących jednak znacznie większe wyzwanie w zakresie projektowania, pomiarów, kontroli i testowania. Przekłada się to na różne problemy występujące w produkcji, a co za tym idzie, rzutuje również na cenę. W technologii 2 nm/18 Ǻ dostarczanie mocy zacznie przesuwać się z przodu chipa na jego tylną stronę, co powinno łagodzić problemy z routingiem, nawet w celu uzyskania wystarczającej mocy do tranzystorów. Poza tym branża prawdopodobnie ponownie zmieni strukturę tranzystorów na złożone tranzystory FET (CFET).

Jak widać, mamy do czynienia z wieloma zmianami procesowymi i strukturalnymi zachodzącymi w krótkim czasie. Należy też zauważyć, że każdy nowy węzeł będzie zawierał coraz więcej problemów, którymi trzeba będzie się zająć.

Przykładem rosnących problemów w przypadku chipów o dużej gęstości upakowania są przejściowe gradienty termiczne. Mogą się one przemieszczać w nieprzewidywalny sposób, czasami bardzo szybko, a innym razem w ogóle. Mogą ponadto zależeć od obciążenia chipa. Efekt ten w technologii 40 nm, przy użyciu grubszych dielektryków i substratów, jest bardzo dokuczliwy. Biorąc pod uwagę dzisiejsze wiodące procesy technologiczne, wszystko to należy traktować znacznie poważniej.

Aktualnie dostępne technologie pozwalają uzyskiwać mniejsze straty ciepła z podstawy niż poprzednie, ale całkowita moc układów jest większa. Wynika to chociażby z większej liczby tranzystorów upakowanych w chipie. Niestety, skutkuje to pogorszeniem wydajności termicznej końcowego wyrobu. Stale rosnące oczekiwania użytkowników elektroniki w zakresie częstotliwości i szybkości działania układów prowadzą do konieczności zwiększania napięć, a zatem i mocy. Staje się ona teraz większa niż w układach starszych generacji. Pojawiają się więc problemy z odprowadzaniem ciepła. Są to efekty szczególnie dokuczliwe na przykład w termowizji.

Zagadnienia termiczne stają się prawdziwym koszmarem każdego inżyniera zajmującego się sprzętem. Można powiedzieć, że uruchamiają pewne błędne koło, które trudno przerwać i zacząć modelowanie od początku. Przykładowo:

- ciepło przyspiesza rozkład warstw dielektrycznych (przebicie dielektryczne zależne od czasu, TDDB – Time-dependent gate oxide breakdown), zwiększa naprężenia mechaniczne, które mogą powodować odkształcenia.

- ciepło przyspiesza elektromigrację i inne efekty starzenia mogące skracać ścieżki danych. W efekcie, ze względu na wyższą rezystancję występującą w obwodach oraz wzrost energii wymaganej do przesyłania sygnałów, rośnie ciepło. Sytuacja taka utrzymuje się, dopóki sygnały nie zostaną przekierowane na inne ścieżki (jeśli to możliwe).

- wymienione efekty mogą mieć wpływ na szybkość działania pamięci, spowalniając ogólną wydajność systemu.

- tworzy się szum mający wpływ na integralność sygnału. Szum może być wprawdzie przejściowy, ale nie ułatwia to zadania inżynierom.

Wszystkie wymienione czynniki mogą skracać żywotność chipa lub jego fragmentów. Nie jesteśmy jednak wobec tych zjawisk bezradni. Możliwe jest przeprowadzenie analizy samonagrzewania się większości elementów wchodzących w skład struktury, chodzi oczywiście głównie o tranzystory. Przejściowe pomiary pozwalają określać temperaturę każdego tranzystora MOS i określać wpływ zlokalizowanych obszarów nagrzewania się na działanie układu.

Obecnie symulacja i modelowanie stały się obowiązującymi etapami każdego projektu inżynieryjnego. Nie dotyczy to zresztą wyłącznie elektroniki. Należy jednak pamiętać, że wynik symulacji jest tak dobry, jak dobre są używane w niej modele. Zatem im lepiej zamodelowany jest każdy materiał interfejsu termicznego, tym większe są szanse na zajęcie się tymi efektami i wprowadzenie odpowiednich zmian w projekcie. W końcowym rozrachunku można w ten sposób unikać zarówno krótkoterminowych, jak i długoterminowych awarii sprzętu. Rzecz w tym, że potrzebne są nowatorskie rozwiązania termiczne i trzeba je odpowiednio zamodelować.

Problemy z zasilaniem

Dotychczasowe technologie produkcji chipów były na tyle proste, jeśli można tak w ogóle powiedzieć, że z powodzeniem stosowało je wielu producentów. Postęp wymusza jednak sięganie po rozwiązania ekstremalne, a to powoduje, że pojawiają się problemy, z którymi technolodzy nie mieli wcześniej do czynienia, przynajmniej w takiej skali jak obecnie. W miarę rosnących wymagań na wydajność systemów coraz częściej stosowane są chiplety, które można porównać do kanapek składających się z wielu struktur umieszczonych na wspólnym podłożu. Warunki pracy takich chipletów są zgoła odmienne od tych, które konstruktorzy znają ze starszych rozwiązań.

Wydaje się, że zwiększenie wydajności układu osiąga się przez zwiększenie gęstości upakowania tranzystorów, czy to w pojedynczym chipie, czy w bardziej zaawansowanej konstrukcji. Nie zawsze jest to zależność oczywista, natomiast zawsze zwiększenie gęstości upakowania elementów wiąże się ze zwiększeniem mocy, a to ogranicza częstotliwość taktowania bloków cyfrowych. W rezultacie, wiele dużych ulepszeń ma jednak charakter peryferyjny i dotyczy samych tranzystorów. Niejednokrotnie też muszą być podejmowane wspólne działania projektowe obejmujące zarówno sprzęt, jak i oprogramowanie. Współpraca obejmuje szereg rozmaitych zagadnień. Optymalizacji podlegają np. fizyczne warstwy sieci i połączenia międzysieciowe. Prowadzone są prace nad zwiększeniem izolacji i ruchliwości elektronów, optymalizowane są operacje pre-fetch pozwalające skracać czas odzyskiwania w przypadku chybionych pobrań. I wreszcie opracowywane są nowe metody dostarczania mocy.

Kluczem do osiągnięcia zamierzonego celu jest zwiększenie wydajności każdego aspektu cyklu projektowania, nie tylko zagadnień dotyczących sprzętu. W branży chipów od kilkudziesięciu lat mówi się o wspólnym projektowaniu sprzętu i oprogramowania, natomiast firmy systemowe nadały takiemu podejściu priorytet dzięki swoim specjalnie zaprojektowanym mikroarchitekturom. Można to łatwo zaobserwować na przykładzie urządzeń mobilnych, których producenci ze względów konkurencyjnych dążą do znacznego wydłużenia czasu pracy baterii.

Jest to jeden element układanki, ale potrzeba ich więcej. Rozważmy na przykład rozkład warstw dielektrycznych w czasie. Może być on przyspieszany na skutek specyficznych warunków pacy, a nawet obciążenia chipu. Efekt jest szczególnie istotny, gdy mamy do czynienia z pakietami wypełnionymi chipletami. Na rozkład warstw dielektrycznych narażone są sieci pracujące z różnymi napięciami .W takim przypadku daje się zaobserwować postępujący w miarę upływu czasu rozkład dielektryka. Jest to nowy problem, który nie został jeszcze rozwiązany.

Niespójności

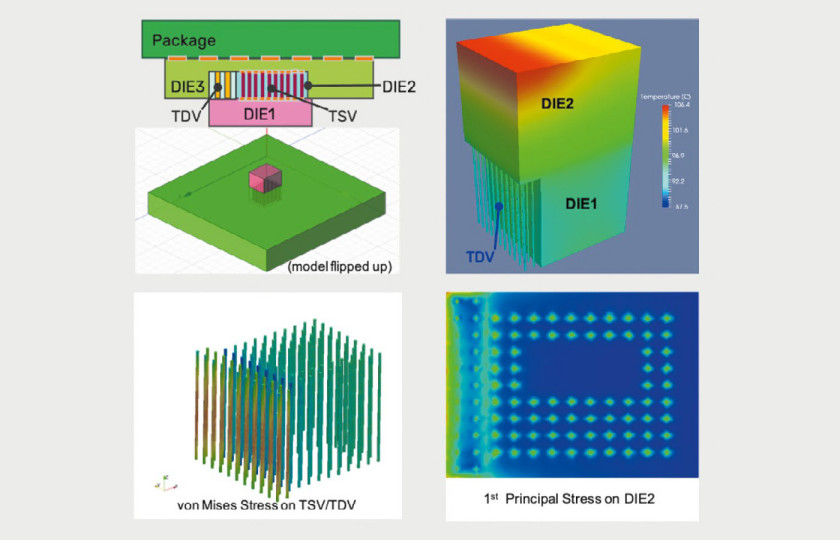

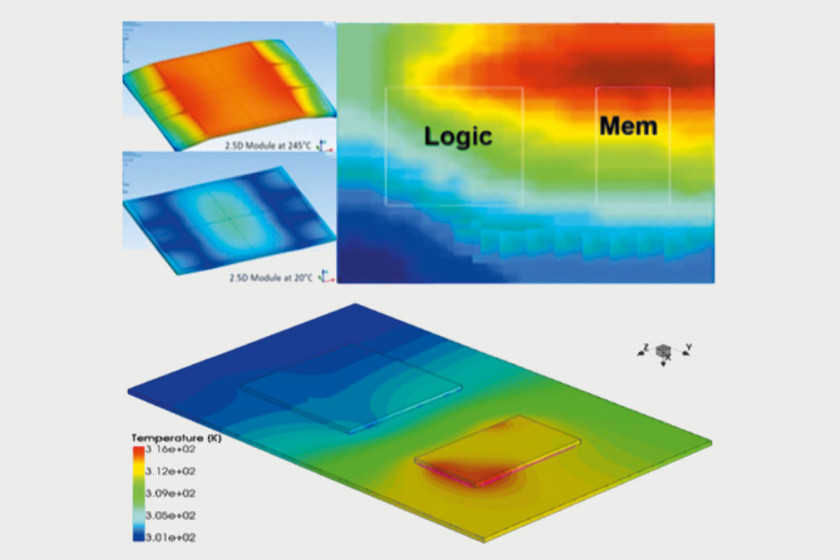

Kolejnym wyzwaniem dla inżynierów są gradienty temperatury. Są one uciążliwe wtedy, gdy występują przejściowo, często różnice występują w zależności od obciążenia układu. Problem ten jest szczególnie dotkliwy w przypadku układów 2.5D, w których gradienty mogą powodować różne odkształcenia. W układach 2.5D wiele chipów jest umieszczanych w tej samej obudowie, tworząc swego rodzaju stos. Pomiędzy poszczególnymi warstwami umieszczane są przekładki umożliwiające wzajemną komunikację. Podobnie będzie z układami 3D-IC, które mają pojawić się w ciągu najbliższych kilku lat. W obu przypadkach ciepło może zostać uwięzione, tworząc efekt tzw. śnieżnej kuli.

Warto wiedzieć, że zużycie energii w układach 3D-IC jest w dużym stopniu powiązane z temperaturą. Wraz ze wzrostem temperatury wzrasta moc strat. W układzie 3D-IC rozkład gradientu termicznego staje się centrum interakcji wielofizycznej. Temperatura wpływa na moc, ale też na występujące w układzie rezystancje. Rosną one wraz ze wzrostem temperatury, a to z kolei wpływa na stałą dielektryczną. Nie pozostaje to obojętne dla integralności sygnału i integralności mocy, wpływa ponadto na naprężenia. A kiedy w układzie 3D-IC mieszane są sygnały cyfrowe i analogowe, sygnał analogowy jest bardziej wrażliwy na obciążenia. Konstruktor musi wiedzieć, gdzie występuje gradient termiczny i gdzie jest zlokalizowany gorący punkt termiczny, ponieważ powinny być od niego odsunięte elementy analogowe. Jeśli obserwowane są cykliczne zmiany temperatury elementu analogowego, można spodziewać się przyspieszonego starzenia się urządzenia. Wydajność obwodu analogowego w porównaniu z układami cyfrowymi gwałtownie spadnie. A jest to dopiero początek dalszych kłopotów.

Nieprawidłowe rozmieszczenie różnych elementów w matrycy ułożonej w stos może powodować nieoczekiwane problemy, takie jak przesłuchy termiczne. Mogą one pogorszyć ogólną wydajność układu.

W konstrukcjach opartych na chipletach poszczególne elementy stosu są umieszczane coraz bliżej siebie, nieuniknione staje się więc wzajemne oddziaływanie. Uzasadnione jest zatem pytanie, jak jest rozprowadzane ciepło, gdy poszczególne warstwy stosu są umieszczane jedna na drugiej? Odpowiedź na nie jest sporym wyzwaniem dla inżynierów. W przypadku układów 3D-IC pierwszą kwestią jest to, czy można zbudować systemy zachowujące integralność strukturalną. Ale są też i inne problemy: mechaniczne, termiczne, energetyczne itp.

W przeszłości najprostszym sposobem zarządzania ciepłem było obniżenie napięcia. Napięcia nie można jednak obniżać w nieskończoność. Po przekroczeniu pewnej granicy najmniejsza nieregularność może powodować problemy.

Przy rozpatrywaniu zagadnień związanych z technologiami urządzeń o bardzo niskim poborze mocy problemem stają się szumy. Jest to tematyka, którą trudno zrozumieć, ponieważ zazwyczaj nie pojawia się w symulacjach. Skutki występowania szumów są obserwowane później w układach rzeczywistych. Dopiero wtedy można i trzeba wszystko zrozumieć i opracować środki zaradcze.

Szum w podłożu może powstawać na przykład na skutek sprzężeń krzyżowych, ale nie zawsze jest to oczywiste na etapie projektowania. W Fraunhofer IIS EAS (niemieckie centrum badawcze zajmujące się badaniami nad systemami mikroelektronicznymi, systemami czujników i systemami automatyki) podjęto próbę stworzenia symulatora podłoża. Prace miały dać odpowiedź na pytanie, jakiego rodzaju sprzężenia krzyżowe występują w podłożu. Nie chodzi przy tym o sprzężenia w pojedynczym urządzeniu i urządzeniach sąsiednich. Rozpatrywane są sprzężenia krzyżowe w stopniu wejściowym, który jest daleko od drugiego stopnia, ale jest sprzężony poprzez podłoże.

Tego typu zagadnienia mogą powodować problemy również w pamięciach DRAM, szczególnie w miarę wzrostu gęstości komórek bitowych, co również powoduje, że są bardziej podatne na szum. Z pewnością występuje w nich szum termiczny. Ponadto, gdy uzyskiwany jest dostęp do ogniwa, tworzy się szum w strukturze spowodowany zakłóceniami elektrycznymi spowodowanymi na przykład przełączaniem połączeń. W tym przypadku również generowany jest szum, który jest przyczyną problemów z niezawodnością. Efekt ten jest nazywany interferencją między komórkami. Mamy tu do czynienia z tzw. problemem młota rzędowego (row hummer problem), polegającym na tym, że wielokrotny dostęp do wiersza w chipie DRAM powoduje przerzucanie bitów (tj. uszkodzenie danych) w fizycznie pobliskich wierszach pamięci. Problem młota rzędowego jest tylko jednym z przykładów występujących trudności.

Pozostając przy pamięciach DRAM, kolejnym przykładem jest efekt RowPress. Występuje on wtedy, gdy jeden wiersz pozostaje otwarty przez zbyt długi czas. W rezultacie powoduje to zakłócenie pracy pozostałych sąsiadujących z nim wierszy. Ten rodzaj interferencji komórek rozpowszechnia się wraz ze zmniejszaniem rozmiaru komórek i umieszczaniem ich coraz bliżej siebie. Mówimy zatem o zwiększaniu ich gęstości.

Nieoczekiwane problemy ujawniają się zawsze, gdy rozpatrujemy zasilanie. Bez względu na częstotliwość taktowania zalecana jest praca przy możliwie najniższym napięciu. Wynika to z faktu, że zużywana jest wtedy najmniejsza energia. Zjawiska związane z zasilaniem mogą być modelowane, ale czasami dają one dość nieoczekiwane wyniki. Podczas modelowania można próbować różnych kombinacji napięć zasilających i częstotliwości pracy układu. Dzięki temu można ustalić warunki optymalne dla danej konfiguracji. Zawsze też można dodać odpowiednie marginesy tak, aby badany chip działał prawidłowo, jednak w ogólnym praktycznym przypadku takie działania nie będą możliwe. Być może rozwiązaniem byłaby klasyfikacja chipów do pewnych kategorii i ustalanie parametrów dla każdej z nich, ale takie podejście też nie daje stuprocentowej pewności optymalnego dobrania warunków pracy dowolnego chipu.

Inne zagadnienia

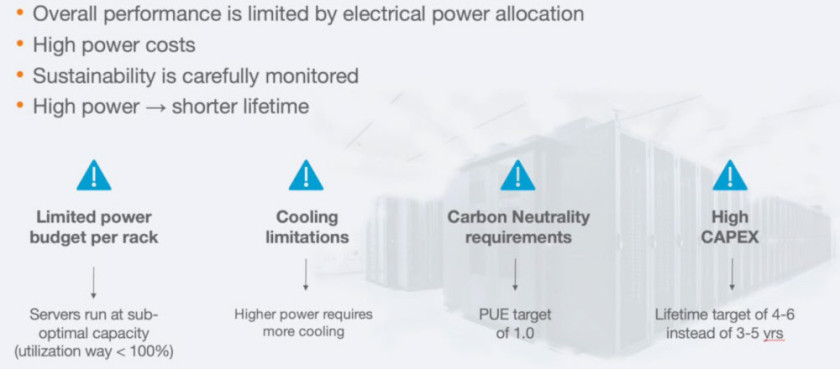

Problemy z energią ujawniają się, gdy rozpatrujemy końcowe rozwiązania. Przykładem niech będą duże serwerownie, centra obliczeniowe i przetwarzania danych itp. Na przestrzeni lat można zaobserwować wykładniczy wzrost pobieranej przez takie jednostki energii. Idąc dalej, można mówić o ich wpływie na środowisko. Chociaż w skali globalnej to zaledwie kropla w morzu, warto chyba robić wszystko, aby wszystkie negatywne oddziaływania minimalizować. Można dzięki nim nie tylko ograniczyć zużycie energii, ale też przedłużyć żywotność elektroniki.

Efekty związane z zasilaniem nie ograniczają się do samego chipa. Gdy mówimy o układach wykonanych w technologii 2,5D, należy brać pod uwagę to, że naprężenia termiczne powodują odkształcenia, które zwiększają ryzyko odrywania kulek łączących podłoże z płytką drukowaną. Wystąpienie takiej usterki może spowodować zwarcie lub przerwę w połączeniach, co będzie skutkowało błędnym działaniem układu lub jego całkowitą awarią. Dlatego ważne jest, jak poradzić sobie z takimi przypadkami i jak je zamodelować w fazie projektowania. A dodać należy, że musi się to wydarzyć na najwcześniejszych etapach pracy, kiedy można jeszcze jakoś zareagować na wykryte zagrożenia.

W układach 3D-IC sprawy stają się jeszcze bardziej skomplikowane. Po raz kolejny nacisk kładzie się na ocenę problemów na początku cyklu projektowego, ale w układach 3D-IC występują efekty addytywne. Dynamiczna moc przełączania jest naprawdę trudniejsza do opanowania w przypadku układów 3D-IC w porównaniu z SoC. Konieczne jest rozpatrywanie architektury fizycznej tak wcześnie, jak to możliwe, ponieważ jeśli rozpatrujemy np. 15 chipletów 3D-IC, należy odpowiedzieć na pytanie, jak podzielić moc pomiędzy nie, aby zapewnić dynamiczne rozłożenie pracy i obciążenie czasowe? Obciążenie chipletu może zmieniać się w różnym czasie, a to może powodować powstanie gorącego punktu termicznego (hotspot). Jeśli jednak zarówno górny, jak i dolny chip mają swoje lokalne hotspoty, to jeśli dwa lokalne hotspoty zrównają się w określonym czasie, wówczas staną się one globalnym punktem termicznym. Jeśli w danym przedziale czasu jeden chip nie przełącza się, może być o 10 lub 15 stopni cieplejszy niż lokalny hotspot. Zaobserwowanie takiego efektu całkowicie zaskoczyło projektantów obwodów 3D-IC. Okazuje się, że prawdopodobnie nie jest możliwe przeprowadzenie emulacji całego chipletu 3D-IC dla warunków odpowiadających warunkom rzeczywistym. Problemem są trudne do opanowania i przewidzenia liczne zależności, które powodują, że nie ma możliwości jakiejkolwiek optymalizacji. Można rozpatrywać jakieś zagadnienie pod kątem właściwości termicznych, takich jak maksymalna temperatura czy rozpraszanie ciepła, ale nie można przy tym pomijać naprężeń mechanicznych. Konieczna jest umiejętność modelowania indywidualnych efektów fizycznych. Jeśli są one ściśle ze sobą powiązane, należy to robić w formie współsymulacji. Przykładem niech będzie prąd płynący przez tranzystor. Spowoduje on oczywiście jakąś reakcję termiczną w postaci wydzielenia pewnej ilości ciepła. Ale ciepło to będzie miało wpływ na własności elektryczne tranzystora, a więc konieczne jest badanie interakcji zachodzącej między tymi parametrami.

Rozwiązania

Nie ma jednego, kompleksowego rozwiązania problemów energetycznych, istnieje natomiast wiele rozwiązań cząstkowych.

Jednym ze sposobów, prawdopodobnie najprostszym, jest ograniczenie przeprojektowania (overdesign), czyli zmniejszenie przyjętych dla celów bezpieczeństwa rezerw parametrów. Wszystko zaczyna się od określenia docelowych warunków użycia układu i zdefiniowania niezbędnych funkcji. Będą one uwzględnione w projekcie. Konstruktorzy zwykle mają chęć dodawania na tym etapie funkcji uwzględniających inne potencjalne przypadki użycia, ale często prowadzi to do zwiększenia powierzchni, mocy i złożoności chipu, co może obniżyć wydajność głównych jego zastosowań. Na wszystkie funkcje należy spojrzeć krytycznie i ocenić je w sposób niemal bezwzględny, aby zrozumieć, czy naprawdę muszą być uwzględnione. Każda nowa funkcja ma wpływ na PPA (Power, Performance, Area), dlatego pierwszym krokiem jest skupienie się na rynkach docelowych i spodziewanych aspektach użycia. Może to mieć znaczący wpływ na całkowite zużycie energii, szczególnie w zastosowaniach związanych ze sztuczną inteligencją. W jej przypadku istnieje wiele opcji do rozważenia, zwłaszcza dla urządzeń brzegowych. Niektóre opcje obejmują sposób zasilania chipa, ograniczenia termiczne, konieczność wspierania uczenia i/lub wnioskowania, wymagania dotyczące dokładności, środowisko, w którym chip będzie wdrażany oraz używane formaty liczb. Obsługa dużych zestawów funkcji oznacza zwiększenie powierzchni i mocy chipa, a także wymusza dodatkowe zwiększenie złożoności blokowania funkcji, gdy nie są używane. Wiemy, że przenoszenie danych wpływa na wydajność i pochłania duże ilości budżetu mocy, projektanci muszą więc dobrze zrozumieć, ile danych powinno być przeniesionych, aby opracować architektury minimalizujące przepływ danych brzegowych.

Inną opcją, szczególnie w przypadku najbardziej zaawansowanych węzłów, jest zasilanie od dołu. W chipletach zasilanie jest często rozprowadzane, począwszy od górnych warstw. To tam jest doprowadzane zasilanie i masa. Jeżeli możliwe jest dołączenie ich do dolnych warstw, połączenia nie muszą przechodzić przez 17 warstw. Może to dać nieoczekiwane korzyści.

Kolejnym podejściem jest umieszczanie w chipach czujników używanych do monitorowania zmian w zachowaniu związanych z zasilaniem, szumem, a nawet starzeniem się struktur. Wszystkie te czynniki wymuszają stosowanie wyższego napięcia, niż jest to konieczne.

Wnioski

Zasilanie stanowiło problem dla wiodących producentów chipów przez ostatnich kilka dekad. Smartfon wyśle ostrzeżenie, że się przegrzewa i wyłączy się, aż do osiągnięcia odpowiednio niskiej temperatury pracy, z tego samego powodu zadania realizowane w jednej szafie serwerów mogą być przekazane do innej szafy. Natomiast coraz częściej chipy są rozkładane na różne komponenty i pakowane razem. Można więc spodziewać się wzrostu problemów z zasilaniem w zastosowaniach związanych na przykład z motoryzacją. Ma to związek z wprowadzaniem chipów wykonywanych w technologii 5 nm i mniejszej.

Architektura, umieszczanie i trasowanie, integralność sygnału, ciepło, niezawodność, łatwość produkcji i starzenie się, to czynniki ściśle powiązane z mocą. Producenci chipów, chcąc docierać do różnych rynków, będą musieli opanować zjawiska związane z zasilaniem lub jakoś je omijać, ale jest to możliwe tylko w nielicznych przypadkach.

Na podstawie: https://semiengineering.com/the-rising-price-of-power-in-chips/

Jarosław Doliński