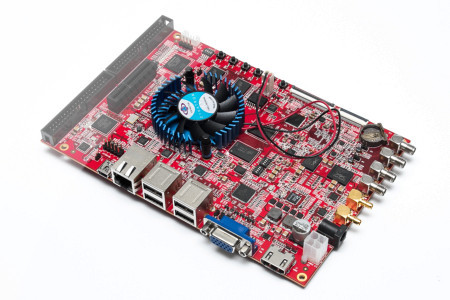

Na płytce Lark znalazł się układ FPGA typu SoC o oznaczeniu 5CSXFC6D6 - największy układ tego rodzaju w rodzinie Cyclone V SX. Zintegrowano w nim procesor FPGA i dwurdzeniowy, w pełni sprzętowy (tzw. Hard Processor System, HPS) procesor ARM pracujący z częstotliwością 800 MHz i połączony z rdzeniem FPGA za pomocą magistrali AXI. W rezultacie uzyskano pojedynczy, monolityczny układ oferujący zarówno wydajność i niskie koszty typowe dla procesorów sprzętowych, jak i elastyczność charakterystyczną dla programowalnych układów logicznych.

- Wprowadzenie na rynek Lark Board dało projektantom możliwość skutecznego korzystania z zalet, wydajności i gęstości upakowania elementów charakterystycznych dla architektury Cyclone V. Innymi słowy, zyskali oni w pełni rozbudowaną, zaawansowaną platformę rozwojową do projektowania i wdrażania systemów wbudowanych - wyjaśniał Joerg Bertholdt, kierownik ds. planowania i marketingu oprogramowania wbudowanego w firmie Altera.

- Jesteśmy zachwyceni tym, że mieliśmy swój udział w opracowywaniu płytki Lark Board. Stanowi ona potwierdzenie wiodącej roli firmy Altera na polu programowalnych układów logicznych i jest zarazem demonstracją naszych możliwości projektowych w zakresie rozwiązań wbudowanych. Inżynierowie z pewnością docenią możliwości, wydajność i elastyczność tego wiodącego zestawu rozwojowego typu SoC, dostępnego przy tym w cenie niespotykanej zwykle w przypadku w pełni wyposażonych płytek ewaluacyjnych z układami FPGA - mówił David Shen, dyrektor techniczny w grupie Premier Farnell.

Lark Board udostępnia obu procesorom, HPS i FPGA, 1 GB pamięci DDR3 SDRAM, a także 4 GB pamięci na karcie eMMC Flash i gniazdo kart pamięci Transflash w charakterze pamięci masowej. Płytka ma wbudowane standardowe interfejsy wejścia-wyjścia, takie jak PCI Express, Gigabit Ethernet, porty hosta USB 2.0, UART, JTAG i 3G SDI. Obsługa ekranów LCD i monitorów z gniazdami HDMI i VGA zapewnia przewagę konkurencyjną.

Na płytce Lark Board znalazł się także dwukanałowy wzmacniacz różnicowy RF/IF 3,3 GHz oraz 12-bitowy, dokładny przetwornik ADC o prędkości 105 MSPS zapewniający wzmacnianie, filtrowanie i próbkowanie sygnałów analogowych. Lark Board wykorzystuje przetwornicę Altera Enpirion, która gwarantuje stabilne zasilanie wszystkich szyn zasilających rozwiązania SoC Cyclone V, a przy tym cechuje się dużą sprawnością.

Na płytce zintegrowano też układ USB Blaster II, zwiększający skuteczność debugowania układu FPGA. Układ ten jest zgodny ze środowiskami programistycznymi Quartus II i ARM DS-5. Lark Board ma też preinstalowaną dystrybucję Linuksa przeznaczoną dla systemów wbudowanych, Yocto, a inne dystrybucje są dostępne do pobrania.

Płytka obsługuje wyświetlacze VGA o rozdzielczości do 1920x1080, a także cyfrowe HDMI w trybie 1080, co czyni ją idealnym rozwiązaniem do zastosowań, w których silnie wykorzystuje się materiały wideo. Ponadto produkt został wyposażony w 30-pinowe złącze kamery, co sprawia, że świetnie nadaje się on do zastosowań z zakresu monitoringu wideo.

Aby przyjrzeć się bliżej platformie Lark board, można wziąć udział w seminarium internetowym "Developing Advanced Embedded Systems with Altera Cyclone V SoC and element14 Lark board", które odbędzie się 2 grudnia 2014 r. Todd Koelling z firmy Altera i Craig Stiegman z element14 pokażą jak wiele opcji konfiguracyjnych i dopasowanych do indywidualnych potrzeb rozwiązań sprzętowych można opracować w oparciu o tę architekturę. Chętni proszeni są o zarejestrowanie się na stronie: www.element14.com/community/events/4223.

źródło: Farnell element14