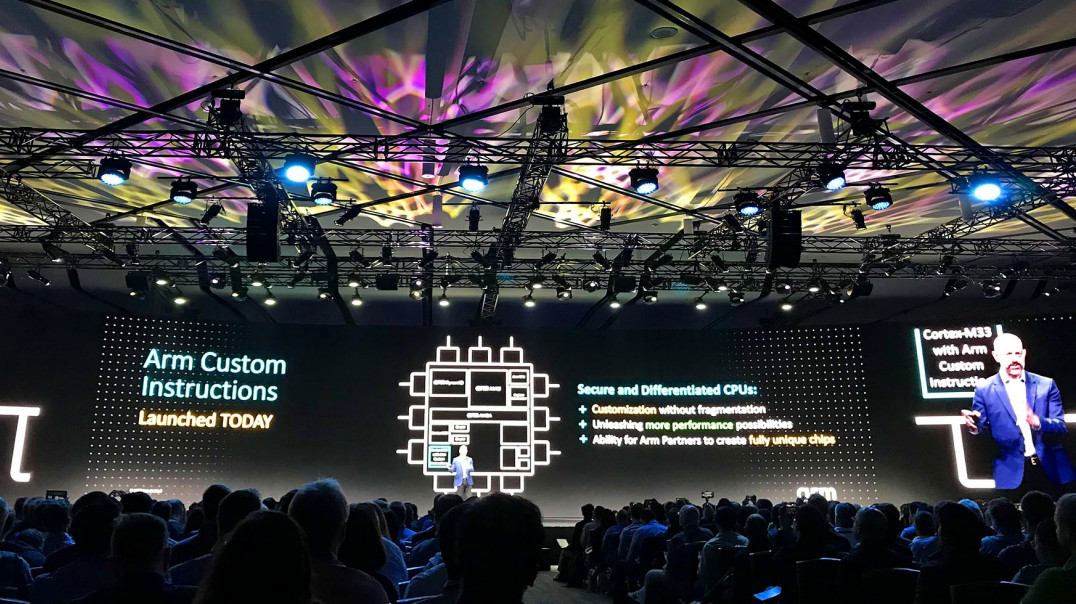

Decyzja o zezwoleniu na wprowadzanie dodatkowych, dostosowanych do indywidualnych potrzeb klientów, instrukcji do architektury ARM ogłoszona została na corocznej konferencji Arm Techcon przez CEO firmy. Zmiana ta otwiera nowy rozdział w polityce tego przedsiębiorstwa, niewątpliwie była też długo wyczekiwana przez wielu klientów firmy.

Według analityków i komentatorów branży ruch ten związany jest zapewne z rosnącą popularnością konkurencyjnych rozwiązań, jak np. RISC-V czy produktów firm Tensilica (obecnie część Cadence) lub ARC (obecnie w składzie Synopsys), które od dawna umożliwiały wprowadzanie indywidualnych instrukcji do swoich procesorów. Co więcej, funkcjonalność taka udostępniana była nawet przez wiekową już architekturę MIPS. Na przykładzie wielu projektów udowodniono, że wprowadzenie nawet jednej dodatkowej instrukcji, dostosowanej do potrzeb aplikacji, pozwala czasem znacząco przyspieszyć wydajność systemu oraz ograniczyć zużycie energii elektrycznej.

Nowa funkcjonalność w pierwszej kolejności wprowadzona zostanie do układów z rodziny Cortex-M. W niedalekiej przyszłości zmiany obejmą również prawdopodobnie układy Cortex-R oraz, być może w dalszej przyszłości, Cortex-A. Przewiduje się, że nowe modyfikacje znajdą zastosowanie głównie w przypadku rdzeni mikrokontrolerów montowanych w większych układach typu SoC, jak również w systemach czasu rzeczywistego. Dobrą wiadomością dla producentów jest na pewno fakt, że modyfikacja listy instrukcji nie będzie dodatkowo płatna.

ARM zapowiedziało również wprowadzenie ekstrakomend oraz mechanizmów bezpieczeństwa dla rdzenia Cortex-A. Ponadstandardowe instrukcje mają na celu głównie przyspieszenie operacji na zbiorach danych, co ma przełożyć się na dużo wyższą wydajność w aplikacjach wykorzystujących algorytmy uczenia maszynowego oraz sieci neuronowych. Dodatkowe mechanizmy bezpieczeństwa mają objąć natomiast m.in. kontrolę korzystania ze wskaźników.

Kilka miesięcy wcześniej ogłoszono również nowe zasady udzielania licencji, co przełożyło się na obniżenie opłat licencyjnych w przypadku niektórych najpopularniejszych IP-Core. Zmiany zmniejszają przede wszystkim koszty wejścia wymagane do uruchomienia produkcji układów, pozwalają również na bardziej elastyczne korzystanie z licencji przez mniejszych wytwórców.

Wielu komentatorów zwraca uwagę, że ARM, ogłaszając nowe plany, odpowiada na żądania i potrzeby rynku oraz klientów w sposób wcześniej raczej niespotykany. Znaczący wpływ mają na to na pewno obecne w przestrzeni rynkowej poważne zagrożenia dla przyszłości firmy, przede wszystkim pod postacią wspomnianego już RISC-V, czyli architektury w wersji open source, niewymagającej żadnych opłat licencyjnych. Obecnie jednak ARM, z liczbą ponad 150 mld wyprodukowanych na ich licencji układów scalonych oraz prognozą podwojenia tego wyniku w ciągu najbliższych dwóch lat, wciąż pozostaje niekwestionowanym głównym dostawcą rozwiązań IP-Core na globalnym rynku. Wprowadzone zmiany powinny pomóc firmie utrzymać pozycję lidera również w dłuższej perspektywie.

Damian Tomaszewski