Niniejszy artykuł przedstawia najpopularniejsze metody dołączania do Ethernetu własnych urządzeń. W części pierwszej prezentowane były podstawowe informacje o standardzie i rozwiązania układowe gotowych konwerterów protokołów i modułów komunikacyjnych, w części drugiej omawiamy Ethernet w mikrokontrolerach i układach programowalnych oraz możliwości dostępnych bibliotek oprogramowania.

Ethernet w mikrokontrolerach

Znalezienie na rynku mikrokontrolerów zawierających zintegrowany kontroler Ethernetu obecnie nie nastręcza większych trudności. Najczęściej dostępna jest jedynie warstwa MAC, więc konieczne jest zastosowanie dodatkowego układu scalonego spełniającego funkcję warstwę fizycznej (PHY). Przykładem układów wyposażonych w warstwę MAC są STM32F107Vx z rodziny STM32 produkowanej przez STMicroelectronics.

Mają one 32-bitowy rdzeń ARM, do 256KB pamięci Flash oraz do 64KB wewnętrznej pamięci SRAM. Zasoby te pozwalają zmieścić w programie obsługę stosu TCP/IP oraz najważniejszych protokołów. Wykorzystanie kontrolera MAC nie odbiega zbytnio od korzystania ze zintegrowanych kontrolerów omówionych wcześniej. Pierwszym krokiem jest wyposażenie urządzenia w warstwę fizyczną (PHY) przez dodanie do projektu stosownego układu scalonego.

Komunikacja między mikrokontrolerem a układem realizującym warstwę fizyczną może się odbywać przez interfejsy MII (Media Independent Interface) lub RMII (Reduced Media Independent Interface). Wysyłanie danych sprowadza się do przygotowania ramki ethernetowej i umieszczenia jej w wewnętrznej pamięci SRAM. Do transmisji przeznaczony został specjalny bufor FIFO o rozmiarze 2KB, do którego dane trafiają z pamięci SRAM za pośrednictwem układu DMA. Stamtąd są przekazywane do modułu PHY i wprowadzane do sieci.

Kontroler warstwy MAC obecny w rodzinie STM32 cechuje się m.in.:

- obsługą transmisji z prędkością 10/100 Mb/s,

- pracą w trybie full-duplex (kontrola przepływu zgodna z IEEE 802.3x) oraz half-duplex (wsparcie dla protokołu CSMA/CD),

- automatycznym wstawianiem i usuwaniem preambuły oraz pola SFD,

- automatycznym obliczaniem sumy kontrolnej CRC.

Nadejście nowej ramki powoduje, że kontroler MAC usuwa z niej preambułę, pole SFD, oblicza sumę kontrolną i przesyła do bufora FIFO dane począwszy od adresu MAC. Możliwość sprzętowego filtrowania odbieranych pakietów pozwala z góry odrzucić niechciane ramki i ograniczyć generowany ruch. Podobne rozwiązania zostały zastosowane w układach rodziny AVR32. Atmel udostępnił sprzętową warstwę MAC umożliwiającą wysyłanie danych z prędkością 10 lub 100Mb/s.

Również w tym przypadku wymagane jest dołączenie zewnętrznego układu PHY. Wymiana danych pomiędzy warstwami MAC oraz PHY jest realizowana z użyciem interfejsu MII lub RMII zależnie od wyboru konstruktora. "Wygodni" konstruktorzy mogą wybrać mikrokontrolery zawierające zintegrowane obie warstwy: MAC oraz PHY. Pozwoli to zrezygnować ze stosowania dodatkowego elementu w projekcie. Wciąż potrzebne będzie gniazdo RJ45, które może mieć wbudowany transformator separujący, co jeszcze bardziej uprości konstrukcję całego urządzenia.

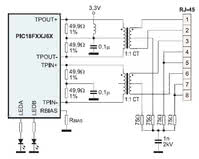

Przykładem mikrokontrolera mającego obie warstwy jest PIC18F97J60 produkowany przez Microchip. Jest on wyposażony w 128KB pamięci programu oraz 3,8kB pamięci RAM, a jego podstawowa, sieciowa aplikacji pokazana została na rysunku 1. Dodatkowe udogodnienie stanowi bufor o pojemności 8KB przeznaczony dla odbieranych i wysyłanych ramek.

Wśród możliwości oferowanych przez zintegrowany kontroler ethernetowy warto wymienić:

- programowalną retransmisję danych po stwierdzeniu kolizji,

- dodawanie bajtów wypełniających (gdy ramka ma za mały rozmiar) oraz generowanie sumy kontrolnej CRC,

- możliwość automatycznego odrzucania uszkodzonych pakietów,

- programowalne filtry pozwalające wyeliminować odbiór niepożądanych pakietów.

Konfigurowanie kontrolera, filtrów oraz dostęp do bufora zostało oparte o zespół rejestrów. Zintegrowany moduł DMA może zostać wykorzystany do kopiowania danych z jednego miejsca do drugiego w obrębie bufora danych oraz do wyznaczania sumy kontrolnej CRC wykorzystywanej przez różne protokoły komunikacyjne (np. TCP, UDP, IP).

Przesyłanie pakietów w mikrokontrolerach PIC18 jest zorganizowane podobnie jak w omówionym wcześniej układzie ENC28J60 i sprowadza się do umieszczenia w buforze pakietu, który ma zostać wysłany, ustawienia wskaźników początku oraz końca ramki i ustawienia odpowiedniego bitu w rejestrze, co wymusi rozpoczęcie transmisji. Dostępne są również mikrokontrolery z rdzeniem ARM zawierające zintegrowane warstwy MAC oraz PHY, czego przykładem mogą być układy z rodziny Stellaris produkowane przez Texas Instruments (np. LM3S9B81).

Producent udostępnił projektantom dwa bufory FIFO (nadawczy oraz odbiorczy) o rozmiarze 2KB pozwalające przechować po jednej pełnej ramce. W sytuacji, gdy ma ona mały rozmiar, do bufora można zapisać większą ich liczbę (do 31). Warto wspomnieć, że suma kontrolna może być wyliczana automatycznie lub zapisywana przez program.

W tym drugim przypadku świadome wysyłanie "uszkodzonych" pakietów pozwoli zbadać zachowanie pozostałych urządzeń pracujących w sieci na okoliczność błędów. Ramki o rozmiarze mniejszym, niż dopuszcza to standard, zostaną automatycznie uzupełnione o brakujące bajty. Zarządzanie pracą warstwy MAC oraz PHY odbywa się za pomocą zespołu rejestrów, natomiast wymiana danych między pamięcią RAM a buforem FIFO może być prowadzona z wykorzystaniem kontrolera μDMA.

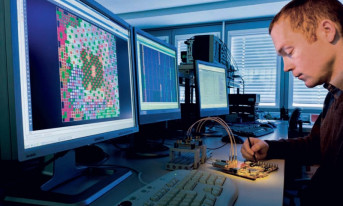

Ethernet w układach programowalnych

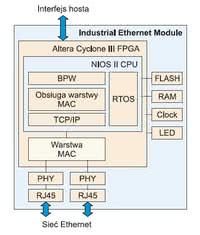

Rys. 2. Schemat blokowy przykładowej realizacji komunikacji sieciowej z wykorzystaniem układu Cyclone III oraz procesora NIOS II

Komunikacja sieciowa jest możliwa również z wykorzystaniem układów programowalnych (FPGA). Oprócz najbardziej intuicyjnego rozwiązania, jakim jest wykorzystanie zewnętrznego kontrolera Ethernet, można zastosować układy FPGA z wbudowanym kontrolerem warstwy MAC lub syntezowalny moduł opisany w języku HDL. W tym drugim przypadku można posiłkować się gotowymi rozwiązaniami lub kreatorami udostępnianymi przez producentów układów FPGA.

Synteza kontrolera MAC może nie być trywialna, jednakże takie podejście pozwala na prostą modyfikację kontrolera MAC i dostosowanie go do nowych standardów bez wprowadzania zmian sprzętowych. Wystarczy przygotować nowy opis, przeprowadzić jego syntezę i na nowo skonfigurować układ FPGA. Niezależnie od wybranego rozwiązania (synteza kontrolera MAC lub wykorzystanie zintegrowanego) niezbędne będzie użycie zewnętrznej warstwy PHY.

Obsługa stosu TCP/IP jest znacznie łatwiejsza za pomocą procesora i oprogramowania niż poprzez przygotowanie odpowiedniego opisu sprzętowego, więc powszechnym podejściem jest synteza rdzenia procesora i uruchamianie na nim oprogramowania. Jego zadaniem jest interpretowanie ramek otrzymanych z warstwy MAC oraz przygotowywanie pakietów, które następnie zostaną przesłane do sieci.

Procesor obsługuje także wyższe warstwy, takie jak TCP/IP, umożliwiając wygodną komunikację z innymi urządzeniami pracującymi w sieci. Na rysunku 2 przedstawiono schemat blokowy tak pracującego systemu. Rdzeń procesora przeznaczony do syntezy w FPGA najłatwiej pozyskać z oficjalnego źródła, jakim jest producent danego układu programowalnego. Na korzyść takiego rozwiązania przemawia duża optymalizacja rdzenia, co przekłada się na wyższą jego wydajność oraz wsparcie w postaci narzędzi do pisania oprogramowania dla danego procesora.

W Internecie dostępne są moduły IP (Intellectual Property) opracowywane przez niezależne jednostki i często udostępniane na zasadach licencji GPL/LGPL. Rozwiązania tego typu można znaleźć np. na stronie www.opencores.org, udostępnione są tam także kontrolery MAC.

Moc obliczeniowa wybranego procesora może być na tyle duża, że pozwoli to uruchomić system operacyjny pokroju Linux czy uC Linux, co jeszcze bardziej uprości komunikację przez sieć Ethernet. Warto zauważyć, że oficjalna dystrybucja jądra Linux zawiera wsparcie dla procesora Microblaze opracowanego przez firmę Xilinx. Tym samym stosunkowo niewielkim kosztem można uruchomić system operacyjny na układzie FPGA.

Listing 1. Szablon programu wykorzystującego stos TCP/IP firmy Microchip// Declare this file as main application file |

Komunikacja Wi-Fi (moduły, routery)

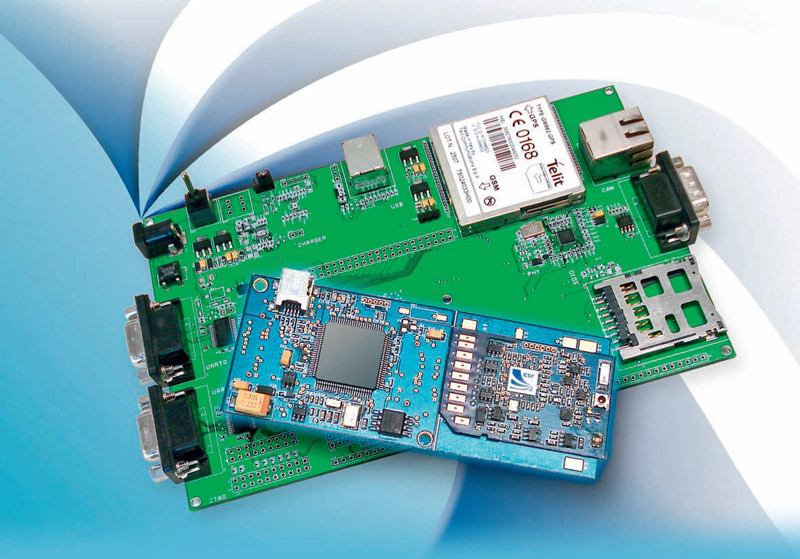

Realizacja bezprzewodowej komunikacji sieciowej z wykorzystaniem sieci WiFi nie musi być trudna, jeżeli wykorzystane zostaną zintegrowane moduły komunikacyjne. Przykładem takiego modułu jest MatchPort b/g produkowany przez firmę Lantronix (rys. 3). Jest to zintegrowane rozwiązanie zawierające 32-bitowy procesor ARM9, pamięć (do 64MB SDRAM i 256MB NAND Flash), nadajnik/odbiornik standardu 802.11b/g, Ethernet 10/100 Mbps, dwa porty szeregowe oraz port USB.

Wśród funkcji modułu warto wymienić wbudowany serwer web, pełną obsługę stosu TCP/IP, wysyłanie przez e-mail informacji o zdarzeniach oraz obsługę protokołów: ARP, UDP, TCP, ICMP, Telnet, AutoIP, DHCP, http czy SNMP. Komunikacja sieciowa może być zabezpieczona protokołami WEP, WPA lub 802.11i/WPA2-Personal. Moduł udostępnia interfejs szeregowy, przez który możliwa jest komunikacja projektowanego urządzenia z siecią Wi-Fi.

Innym przykładem układu do komunikacji przez sieć Wi-Fi jest moduł MRF24WB0MA produkowany przez firmę Microchip. Jest on zgodny ze standardem 802.11b/g/n i zapewnia komunikację z prędkością 1 oraz 2 Mbps w odległości do 400m. Zintegrowana antena oraz małe wymiary (21×31mm) umożliwiają łatwiejsze wbudowanie układu do własnego projektu.

Moduł podczas pracy musi być zasilany napięciem z zakresu od 2,7 do 3,6V, a typowy pobór prądu wynosi: 85mA (odbiór) oraz 154mA (nadawanie). Producent wyposażył produkt w sprzętową kontrolę dostępu do medium transmisyjnego (CSMA/CA), automatyczne wysyłanie potwierdzeń oraz sprawdzanie i dodawanie sumy kontrolnej. Warstwa MAC może ponadto samodzielnie retransmitować ramki, jeżeli zajdzie taka potrzeba.

Bezpieczeństwo transmisji zapewnia obsługa protokołów WEP, WPAPSK oraz WPA-2-PSK oraz zintegrowane, sprzętowe moduły szyfrujące zapewniające wsparcie dla algorytmów AES oraz RC4. Interfejs od strony mikrokontrolera stanowi port SPI, linia CS oraz dodatkowe linie sterujące (przerwanie, reset, stan hibernacji). Dla łatwiejszego debugowania dodane zostały porty JTAG i UART.

Z oczywistych względów moduł jest szczególnie polecany do współpracy z mikrokontrolerami PIC (PIC18, PIC24, dsPIC33 oraz PIC32). Współpraca z innymi rodzinami układów nie będzie łatwa do zrealizowania, gdyż znajdująca się na stronie produktu dokumentacja nie dostarcza opisu wewnętrznych rejestrów oraz sposobu konfiguracji modułu.

Zadanie to zostało powierzone bibliotekom opracowanym przez Microchip (Microchip Application Libraries, w skład której wchodzi także stos TCP/IP) dla mikrokontrolerów z rodziny PIC. Jest to rozwiązanie z jednej strony wygodne, gdyż moduł jest od początku tworzony z myślą o obsługiwaniu przez gotowe biblioteki, co pozwoli znacząco zaoszczędzić czas projektantów, jednakże z drugiej strony wymusza stosowanie mikrokontrolerów tylko jednej firmy, co nie zawsze jest rozwiązaniem korzystnym.

Dokumenty RFCDokumenty RFC (Request for Comments) są publikowane przez nieformalne, międzynarodowe stowarzyszenie IETF (Internet Engineering Task Force). Zawierają one definicje znaczącej części standardów oraz protokołów internetowych (np. TCP, IP, DHCP). Dokumenty te nie stanowią same w sobie standardu, ale z czasem część z nich jest przekształcana w oficjalne standardy sieciowe. Idea dokumentów RFC została zapoczątkowana w roku 1969 i od samego początku obowiązuje zasada, że raz opublikowany dokument nie jest później zmieniany. Wszelkie pomyłki koryguje się poprzez wydawanie poprawek, natomiast błędne rozwiązania są anulowane i w ich miejsce wydawany jest nowy dokument RFC. Takie podejście sprawiło, że powstała interesująca historia Internetu, którą można prześledzić, analizując kolejne zapisy na stronie IETF. Analiza taka pokaże, w jaki sposób następowała ewolucja sieci na przestrzeni kilkudziesięciu lat. Stowarzyszenie IETF ma charakter otwarty i nie ma osobowości prawnej. W strukturze organizacyjnej można wyróżnić m.in. grupy robocze mające własne grupy mailowe, do których mogą zapisywać się nowi członkowie. W ramach takiej grupy wypracowywane jest wspólne stanowisko w danej sprawie lub kilka różnych z zaznaczonym procentowym poparciem dla każdego z nich. Następnie stanowisko takie jest przekazywane do ciała decyzyjno- koordynującego IESG (Internet Engineering Steering Group), które może zatwierdzać lub odrzucać w drodze głosowania propozycję dokumentu RFC. |

Biblioteki do obsługi stosu TCP/IP

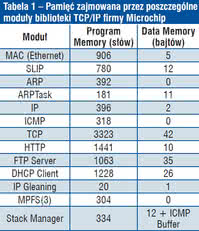

Przykładem firmy udostępniającej bezpłatnie stos TCP/IP dla produkowanych przez siebie mikrokontrolerów jest Microchip. Biblioteka ta współpracuje z układami PIC (PIC18, PIC24, dsPIC oraz PIC32). Stos napisano w języku C w sposób modułowy, co pozwala dołączyć do programu jedynie potrzebne funkcje i ograniczyć ilość wymaganej pamięci, a każda warstwa wykorzystuje interfejs udostępniany przez warstwy niższe.

Producent zadbał, aby użycie oprogramowania we własnych projektach nie wymagało zagłębiania się w tajniki protokołów sieciowych. Biblioteki zapewnia obsługę protokołów takich jak ARP, IP, ICMP, UDP, TCP, DHCP, SNMP, HTTP, FTP, TFTP i pozwala łatwo zrealizować najpopularniejsze usługi sieciowe, np. serwer HTTP, obsługę poczty elektronicznej.

Należy jednak mieć na uwadze, że stos opracowany przez Microchipa wymaga pracy "asynchronicznej", aby na bieżąco monitorować stan warstwy MAC i reagować na zaistniałe zdarzenia: pojawienie się nowego pakietu, przekroczenie dopuszczalnego czasu oczekiwania. Zrezygnowano tu z implementacji systemu operacyjnego na rzecz wielozadaniowości bez wywłaszczania procesów (Cooperative Multitasking).

Oznacza to, że każdy uruchomiony "proces", którym w istocie będą funkcje biblioteczne stosu i funkcje użytkownika, może być wykonywane przez określony, krótki czas. Następnie ich wykonanie kończy się, a kolejny proces może zostać uruchomiony i wykonać powierzone mu zadanie. Wszystkie takie procesy są umieszczane wewnątrz nieskończonej pętli, co sprawia, że są wykonywane jeden po drugim przez cały czas pracy mikrokontrolera.

Szablon programu z główną funkcją main zawierającą działający w ten sposób stos TCP/IP można zobaczyć na listingu 1, natomiast w tabeli 1 wyszczególniono zapotrzebowanie na pamięć programu i RAM przez poszczególne moduły biblioteki. Inną firmą dostarczającą bibliotekę do obsługi protokołów TCP/IP jak InterNiche Technologies posiadająca w swojej ofercie stos NicheLite.

Kod został zoptymalizowany pod kątem zajmowanej pamięci programu (podstawowa biblioteka wymaga jedynie 12KB) oraz łatwości adaptacji do różnych rodzin mikrokontrolerów. Oprogramowanie napisano w języku C i jest zgodne z wytycznymi zawartymi w dokumentach RFC. Warto dodać, że użyta organizacja buforów upraszcza zarządzanie pamięcią i pozwala uniknąć kopiowania danych pomiędzy różnymi jej obszarami.

Wśród obsługiwanych protokołów można wymienić: ARP, IP, ICMP, UDP, TCP, DHCP, BOOTP czy TFTP. Obsługiwane są pakiety IPv4 oraz IPv6. Podstawowa wersja stosu może zostać wzbogacona o dodatkowe moduły realizujące obsługę usług takich jak: HTTP, FTP, Telnet, DHCP, SNMP czy poczta elektroniczna.

Na stronie producenta udostępniono przykłady wykorzystania stosu NicheLite w wybranych zestawach ewaluacyjnych przeznaczonych dla układów: STR912, LM3S9B90, LPC23xx czy Nios II (procesor syntezowany w układach FPGA firmy Altera). Stos TCP/IP (μC/TCP-IP) przeznaczony dla układów 16-, 32-, a nawet 64-bitowych układów dostarcza również Micrium. Rozwiązanie tej firmy powstało z myślą o systemach wymagających dużej niezawodności i odporności na błędy.

Przykładowym obszarem zastosowań, o którym wspomina producent, jest awionika. Aplikacje kierowane dla tego obszaru zastosowań wymagają certyfikacji. Stos μC/TCP-IP, według zapewnień Micrium, jest przygotowany do uzyskania stosownych poświadczeń niezawodności. Warto zwrócić uwagę na skalowalność stosu pozwalającą włączyć do projektu jedynie biblioteki realizujące wymagane funkcje bez konieczności kompilowania całego kodu źródłowego.

Przekłada się to na zmniejszenie rozmiaru kodu wynikowego, co w połączeniu z dbałością o optymalne wykorzystanie pamięci RAM pozostawia projektantom więcej zasobów do dyspozycji. Rozmiar bufora pakietów można dostosować do konkretnych wymogów aplikacji, a nie do maksymalnego rozmiaru ramki, co przyczynia się do dodatkowych oszczędności zasobów.

Ma to znaczenie zwłaszcza dla systemach wbudowanych, w których przesyłane są pakiety zawierające niewielką ilość danych. Prawidłowa praca μC/TCP-IP jest uzależniona od obsługi zaawansowanych mechanizmów podziału zadań (task scheduling) oraz zapobiegania jednoczesnego dostępu do zasobów przez więcej niż jeden proces (mutual exclusion), co zasadniczo narzuca konieczność wykorzystania systemu operacyjnego czasu rzeczywistego (RTOS).

Najprostszym wyjściem będzie wykorzystanie systemu μC/OS-II lub μC/OS-III opracowanego również przez Micrium, ale przewidziano możliwość dostosowania innych systemów do współpracy ze stosem μC/TCP-IP. Warto dodać, że stos opracowany przez Micrium może być rozbudowany o dodatkowe moduły (np. μC/DHCP, μC/FTP, μC/HTTP czy μC/POP3) pozwalające zrealizować obsługę popularnych usług sieciowych.

Podsumowanie

Rozwój sieci i Internetu na przestrzeni ostatnich lat sprawił, że Ethernet jest jednym z najważniejszych kanałów komunikacyjnych między komputerami, a ostatnimi czasy zyskuje także na znaczeniu w przypadku innych urządzeń elektronicznych. Szeroki wachlarz rozwiązań pozwalających zapewnić komunikację tą drogą we własnych projektach pozwala sądzić, że ekspansja sieci będzie postępowała dalej.

Na korzyść Ethernetu przemawia przede wszystkim infrastruktura, która jest bardzo mocno rozwinięta i często bez układania dodatkowej instalacji można przyłączyć własny układ do większego systemu. Nie bez znaczenia jest też dostępność stosów TCP/IP pozwalających zrealizować wymianę danych w sposób wygodny, bez potrzeby zagłębiania się w funkcjonowanie niższych warstw.

Nieodłączną cechą jest również pewność komunikacji, gdyż protokół TCP zawiera szereg mechanizmów gwarantujących poprawne dostarczanie danych wysyłanych do innego urządzenia. Duża liczba publikacji oraz przykładów pozwala dokładnie zapoznać się z funkcjonowaniem sieci także od strony praktycznej i ułatwia implementację Ethernetu we własnych produktach. W sytuacji, gdy koszt końcowego urządzenia nie jest krytyczny, można skorzystać z gotowych modułów, które funkcje sieciowe realizują samodzielnie, a konstruktorom udostępniają jedynie proste, znane interfejsy, takie jak RS232 czy SPI.

Jakub Borzdyński