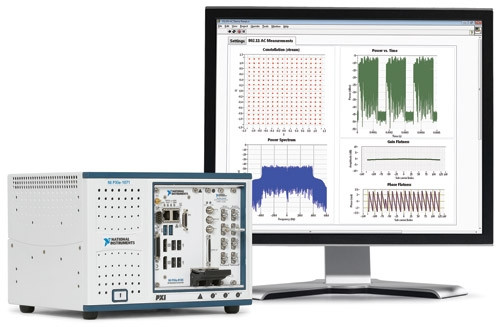

Przyrząd VST (Vector Signal Transceiver) został zaprojektowany w standardzie PXI Express i zajmuje w obudowie szerokość trzech modułów (rys. 1). Konstrukcja modułowa pozwala na tworzenie konfiguracji pomiarowych typu MIMO (wiele wejść, wiele wyjść), poprzez użycie wielu takich samych przyrządów VST umieszczonych we wspólnej obudowie.

Atutem nowego urządzenia jest z pewnością wysoka wydajność niezbędna do prowadzania prac w działach badań i rozwoju oraz niewielkie wymiary zewnętrzne. Wraz z możliwością przeprogramowywania funkcjonalności, zapewnianą przez układ FPGA pozwala to na przyspieszenie wykonywania zadań pomiarowych takich jak charakteryzacja, weryfikacja, walidacja i testy produkcyjne. VST pracuje w zakresie od 65 MHz do 6 GHz z pasmem przenoszenia do 80 MHz.

Od strony funkcjonalnej największą zmianą, zasługującą w pełni na określenie rewolucyjna, jest wbudowana macierz FPGA Virtex-6 LX195T firmy Xilinx, która może być programowana z poziomu oprogramowania LabVIEW FPGA Module. Układ FPGA jest podłączony do cyfrowych sygnałów I/Q w blokach VSA i VSG i dodatkowo do 24 linii I/O zapewniających szybkość transmisji do 250 Mbit/s.

Taka konfiguracja pozwala na wykorzystanie urządzenia w wielu różnych aplikacjach czasu rzeczywistego: do sterowaniem badanym urządzeniem podczas testów, do generowania i odbioru sygnałów radiowych w aplikacjach SDR (Software Defined Radio), emulacji kanałów radiowych w komunikacji bezprzewodowej i wielu innych zastosowań.

Architektura bloku FPGA

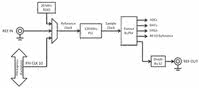

Blok FPGA transceivera VST PXIe-5644R zawiera układ Virtex-6, układ taktowania dla cyfrowego generatora sygnału baseband, pamięć DRAM i SRAM, przetworniki analogowo-cyfrowe (ADC) i cyfrowo-analogowe (DAC), cyfrowe linie I/O (PFIO), cyfrowe złącze komunikacyjne (DIO) oraz linie komunikacyjne podłączone do magistrali PXI.

Układ FPGA jest odpowiedzialny za obróbkę danych cyfrowych w urządzeniu VST i jest bezpośrednio połączony z przetwornikami, magistralą PCI Express, pamięciami oraz liniami interfejsu cyfrowego. Program sterujący dla FPGA może zostać stworzony przez użytkownika samodzielnie za pomocą LabVIEW, można też skorzystać z przykładowych projektów dostarczanych przez producenta oraz z tzw. Instrument Design VI.

Pozwalają one użytkownikom na dostęp i modyfikowanie kodu LabVIEW na poziomie procesora i FPGA (np. na PC lub z systemu operacyjnego czasu rzeczywistego) i zmiany w zakresie konfiguracji, akwizycji, generacji, przetwarzania sygnałów cyfrowych i ich synchronizacji.

Taktowanie

Transceiver VST posiada wiele wewnętrznych źródeł taktowania dostępnych z poziomu FPGA. Główny sygnał zegarowy 120 MHz jest generowany za pomocą pętli PLL i wykorzystywany do taktowania przetworników i logiki powiązanej z FPGA. Poza tym można korzystać z wewnętrznego generatora TCXO, wejścia RF IN na panelu czołowym lub użyć z zegara PXI_CLK 10 jako sygnału odniesienia dla pętli PLL.

Analogicznie główny sygnał zegarowy stanowi odniesienie dla wyjść RF IN i OUT. Mimo że jego częstotliwość jest niezmienna i ustalona na 120 MHz, mamy możliwość dzielenia lub mnożenia tego sygnału implementując odpowiedni kod na FPGA. Daje to dostęp do częstotliwości taktowania do 360 MHz.

Przetworniki i interfejsy

Transceiver VST wykorzystuje dwukanałowe 16-bitowe przetworniki ADC i DAC taktowane zegarem 120 MHz, co umożliwia obróbkę sygnału w paśmie 80 MHz. Ich działanie jest automatycznie synchronizowane z opisanym powyżej głównym zegarem taktującym dostępnym w FPGA. Takie podłączenie ułatwia wymianę danych i ich synchronizację oraz zapewnia przewidywalne opóźnienie w czasie transmisji, co jest ważne w testach aplikacji wbudowanych, takich jak radio definiowane programowo (Software Defined Radio - SDR).

Z kolei PFI 0 to dwukierunkowy, 3,3-woltowy port cyfrowy ogólnego przeznaczenia. Jest on zwykle wykorzystywany jako wejście wyzwalające lub wyjście do generacji znaczników czasu lub zdarzeń. Funkcja, jaką w systemie pełni PFI 0, jest programowana z poziomu LabVIEW.

24-cyfrowe dwukierunkowe linie I/O LV TTL mogą być konfigurowane i organizowane w oddzielne porty. Mamy do nich dostęp bezpośrednio z FPGA, dzięki czemu mogą być wykorzystane do implementacji własnych rozwiązań z poziomu modułu LabVIEW FPGA.

Pamięci DRAM i SRAM

W urządzeniu zawarto dwa banki pamięci DRAM o rozmiarze 256 MB każdy o teoretycznej przepustowości 2,1 GB/s. Każdy z nich jest dostępny z FPGA i zwykle wykorzystywany do przechowywania obwiedni generowanych przebiegów lub danych z przetworników bezpośrednio po akwizycji. Ponadto wbudowano 2 MB pamięci SRAM o maksymalnej prędkości transmisji 40 MB/s do odczytu i 36 MB/s do zapisu, która zapewnia przesyłanie danych pomiędzy poszczególnymi blokami funkcjonalnymi, np. wykorzystuje się ją do konwersji pomiędzy danymi w formacie IQ a ich reprezentacją cyfrową.

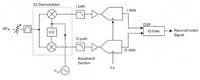

Architektura odbiornika

Odbiornik wykorzystuje architekturę homodynową, czyli przemianę częstotliwości z zerową częstotliwością pośrednią. Taki sposób konwersji sygnału w.cz. nazywa się także bezpośrednią konwersją częstotliwości. Wejściowy sygnał w.cz. jest podawany do mieszacza jak w odbiorniku heterodynowym, z tym że częstotliwość oscylatora lokalnego jest taka sama, jak częstotliwość sygnału wejściowego, przez co produkt mieszania jest sygnałem o niskiej częstotliwości i może być przetwarzany bezpośrednio przez przetwornik ADC. Następnie jest on przekształcany na składowe I (inphase) i Q (quadrature), przesunięte w fazie o 90° i dalej zamieniany na formę cyfrową w przetworniku.

Zaletą architektury homodynowej jest prostota układowa, niski pobór mocy i wysoka selektywność, zapewniająca wysoką separację sygnału pożądanego. Przy współpracy odbiornika homodynowego z pojedynczym przetwornikiem ADC użyteczne pasmo przetwarzania sięga około 40% częstotliwości próbkowania, niemniej w przypadku architektury homodynowej współczynnik ten jest dwa razy większy, bo do obróbki sygnału wymagane są dwa przetworniki.

Dodatkowo układy o mniejszej maksymalnej częstotliwości próbkowania mają lepszy współczynnik szumów i zakres dynamiki SFDR. Innymi słowy, dwa słabsze przetworniki dają lepsze parametry niż pojedynczy szybki przetwornik w innej architekturze odbiornika.

Pojedynczy oscylator lokalny występujący w tym rozwiązaniu wykorzystywany jest w generatorze i analizatorze. Konstrukcja układowa dzięki temu jest prostsza, łatwiej też zachować wysokie parametry i powtarzalność, co jest kluczowym czynnikiem wysokiej jakości działania urządzenia pomiarowego w zastosowaniach typu MIMO.

Układ elektroniczny ma mniej drogich elementów w.cz. i filtrów, przez co jest prostszy i tańszy w produkcji.

Wadą odbiornika homodynowego jest natomiast niemożliwość realizacji układu detekcji obwiedni. W urządzeniu PXIe-5644R problem ten został rozwiązany za pomocą detektora kwadraturowego i cyfrowej obróbki sygnału po demodulacji.

Kolejnym problemem jest offset DC wywołany zerową częstotliwością pośrednią. Mieszanie sygnału w taki sposób umieszcza widmo sygnału zdemodulowanego wokół zerowej częstotliwości, a niedokładności w częstotliwościach generatorów wywołują powstawanie składowej stałej, która musi być zerowana za pomocą specjalnej procedury kalibrującej.

Na rysunku 6 pokazana została architektura stopnia wejściowego odbiornika, zawierająca syntezer kalibracyjny, opcjonalny dzielnik dla sygnałów dużej mocy i wzmacniacz dla słabych sygnałów, zestaw filtrów dolnoprzepustowych wydzielających użyteczny sygnał, układy kondycjonowania sygnału, demodulator i trzy mieszacze (w zależności od częstotliwości pracy wykorzystywany jest ten, który zapewni najlepsze wzmocnienie i parametry fazowe). Blok filtrów zawiera osiem różnych wersji pasmowych oraz dolnoprzepustowych. Ich zadaniem jest głównie eliminacja szumów.

Dzielniki wykorzystywane w torze odbiornika zapewniają tłumienie do 80 dB regulowane co 1 dB, z kolei układ kondycjonowania sygnału bazuje na trzech przełączanych wzmacniaczach zapewniających możliwość rozszerzenia zakresu dynamicznego i poprawy współczynnika szumów.

Konstrukcja odbiornika VST bazuje na jednostopniowym mieszaczu. Wejściowy sygnał w.cz. jest mieszany z sygnałem z oscylatora lokalnego o takiej samej częstotliwości, dzięki czemu wyjściowy sygnał może być bezpośrednio przetwarzany przez przetwornik ADC z szybkością próbkowania 120 MS/s i słowem 16-bitowym.

Zapewnia to szerokie pasmo przetwarzania, dobre tłumienie sygnałów lustrzanych i minimalne przenikanie sygnału oscylatora na wejście miernika. Oscylator lokalny jest układem wspólnym dla wielu mieszaczy, a jego sygnał wyjściowy charakteryzuje się niskim szumem fazowym, co jest istotne w systemach MIMO, gdzie stałość fazy ma decydujące znaczenie dla równolegle prowadzonej akwizycji sygnału w wielu torach odbiorczych.

Poza trybem pracy z zerową częstotliwością pośrednią, przyrząd może działać w trybie z niską częstotliwością pośrednią. Wówczas częstotliwość oscylatora lokalnego leży powyżej pasma sygnału wejściowego, co uwalnia od problemów z pojawiającą się składową stałą na wyjściu mieszacza, a także szumem 1/f i zniekształceniami harmonicznymi. Możliwość wyboru trybu pracy zapewnia wysoką elastyczność i daje możliwość unikania negatywnych czynników związanych z przemianą częstotliwości w konkretnym przypadku.

Architektura nadajnika

Tor nadajnika w transceiverze VST bazuje na dwóch modulatorach, zestawie filtrów i układach kondycjonujących (rys. 7). Modulatory mają konstrukcję zoptymalizowaną pod kątem sparowania ich charakterystyki fazowej i amplitudowej w zakresie częstotliwości pracy. Blok filtrów jest taki sam, jakiego użyto w odbiorniku, a więc z filtrami pasmowymi i dolnoprzepustowymi.

Po filtracji sygnał w.cz. podawany jest do bloku kondycjonowania zawierającego programowalne dzielniki (do 100 dB tłumienia ustawianego co 1 dB), jeden wzmacniacz o regulowanym wzmocnieniu i dwa o wzmocnieniu stałym, co pomaga z kolei uzyskać sygnały wyjściowe o dużej mocy. Na koniec gotowy sygnał jest załączany do wyjścia na panelu przyrządu lub podawany do gniazda kalibracyjnego.

Nadajnik zawiera także mieszacz, którego zadaniem jest przesunięcie sygnału baseband z zakresu niskich częstotliwości, jakie uzyskuje się na wyjściu przetwornika DAC, do pasma w.cz. Jest to realizowane poprzez wymieszanie sygnału baseband z sygnałem z generatora lokalnego.

Podobnie jak w przypadku odbiornika przemiana częstotliwości jest bezpośrednia, czyli sygnał z generatora lokalnego jest równy częstotliwości sygnału w.cz. z generatora. Zapewnia to dobre tłumienie sygnału lustrzanego i niskie przenikanie sygnału z generatora lokalnego na wyjście. Podobnie jak w przypadku odbiornika, jeden generator lokalny może obsłużyć kilka nadajników w układach MIMO.

Oscylator lokalny pracuje w zakresie częstotliwości od 65 MHz do 6 GHz z rozdzielczością 1 Hz w układzie syntezera częstotliwości. Podstawą czasu dla syntezera jest sygnał 120 MHz, który stanowi odniesienie dla trzech generatorów VCO pracujących w zakresie 2-2,5 GHz, 2,5-3 GHz i 3-4 GHz. Dla sygnałów wyjściowych poniżej 4 GHz wykorzystywane są dzielniki częstotliwości, dla sygnałów z zakresu 4-6 GHz używany jest podwajacz, a następnie filtr eliminujący harmoniczne wynikające z podwajania.

Współczynnik szczytu i średnia moc wyjściowa

Współczynnik szczytu podaje stosunek wartości maksymalnej (szczytowej) do wartości skutecznej (RMS) sygnału. Dla sinusoidy wynosi 3 dB co znaczy, że moc skuteczna sygnału jest o 3 dB, mniejsza niż maksymalna. Im sygnał bardziej odbiega od fali prostokątnej, tym jego współczynnik szczytu jest większy, np. dla modulacji ODFM wynosi od 10 do 12 dB.

Trzeba pamiętać o tych zależnościach przy ustalaniu poziomu wyjściowego z generatora. Maksymalna średnia moc wyjściowa wynosi 6 dBm, a obsługiwany współczynnik szczytu wynosi maksymalnie 12 dB. Przekraczanie wartości maksymalnych może skutkować nasyceniem wzmacniacza wyjściowego i wzrostem zniekształceń.

Czystość widmowa

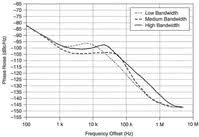

Obecność mieszacza w torze sygnałowym nadajnika i odbiornika może prowadzić do trudnych do wyeliminowania interferencji podczas mieszania sygnału wejściowego z generatorem lokalnym, gdy widmo tego ostatniego nie będzie czyste. Przyrządy pomiarowe na zakres w.cz. bazują na generatorach, w których częstotliwość jest syntezowana w pętli PLL, dlatego od jakości tego bloku zależy wiele kluczowych parametrów przyrządu. Stąd do konstrukcji PXIe-5644R wykorzystano własne, zoptymalizowane rozwiązanie układowe tego bloku, zamiast gotowego bloku dostępnego na rynku w formie modułu.

Syntezer PLL pracuje w trzech trybach różniących się szerokością pasma pętli sprzężenia zwrotnego. Szerokie pasmo zapewnia krótki czas ustalania częstotliwości wyjściowej, rzędu 250 μs, ale i wyższe szumy fazowe. Średniej szerokości wartość pasma daje nieco wyższy czas ustalania (500 μs) i dobre szumy fazowe. Wąskie pasmo zapewnia bardzo niskie szumy fazowe, kosztem wysokiego czasu ustalania (synchronizacji pętli) rzędu 1 ms.

Średniej szerokości pasmo jest wymagane przy testowaniu sieci bezprzewodowych takich jak LTE lub 802.11ac, ale gdy pomiary nie muszą być szybko prowadzone, można też posłużyć się pasmem wąskim. Szerokie pasmo to domena testów systemów z modulacją ze skokowo zmienianą częstotliwością. Na rysunku 8 pokazano, jak zmienia się szum fazowy syntezera w zależności od wybranej szerokości pasma.

Kalibracja

Każdy transceiver PXI-5644R posiada wyprowadzenia wewnętrznego kalibratora połączone przewodem w momencie kalibracji fabrycznej. W jej trakcie sprawdzane są kluczowe parametry takie, jak wzmocnienie w obwodach oscylatora lokalnego, wzmocnienie toru w.cz. w nadajniku i odbiorniku, tłumienie sygnałów lustrzanych i minimalizacja przenikania sygnału oscylatora lokalnego na wejście i wyjście.

Erik Johnson, product manager - RF and Wireless Test

National Instruments

poland.ni.com