Rys. 1. Symulatory ESD wprowadzają ukształtowane w przebiegu czasowym impulsy o znormalizowanym napięciu i prądzie

Metody kwalifikacji zostały udoskonalone, ale aktualne techniki testowania nie dają dostatecznego wglądu w sposób, w jaki wbudowane w system podzespoły reagują na ESD. Słabe sygnały modeli IBIS (Image Based Information System) czy symulacji integralności sygnału nie wystarczają, nie odzwierciedlają bowiem zachowania układów poddanych ESD lub innym rodzajom przeciążeń elektrycznych.

Wywołane przez ESD przebiegi prądowe mogą być wykrywane skanowaniem, ale do jego przeprowadzenia badane układy muszą być częściowo demontowane. Zatem rzeczywiste działanie systemu zostaje zaburzone na czas skanowania. Nowa technika, nazwana skanowaniem wewnętrznym (embedded scanning), obiecująco zmienia ten stan rzeczy, ponieważ obwód testujący jest umieszczany bezpośrednio w układzie scalonym.

Typowe testy podatności wstępnej i podatności własnej systemu zazwyczaj polegają na poddawaniu badanego układu powtarzalnym przebiegom ESD za pomocą symulatorów. Symulatory te wytwarzają znormalizowane sygnały ESD, które mogą zawsze zakłócić działanie lub uszkodzić niemal każde urządzenie albo system elektroniczny, wyznaczając w ten sposób granice jego wrażliwości i niezawodności.

Kwalifikacja systemu polega na sprawdzeniu, czy wytrzymuje on dopuszczalny poziom albo czy ulega uszkodzeniu po przekroczeniu tego poziomu o wybrany margines. Rysunek 1 przedstawia typowy pistolet symulatora ESD, stosowanego do przeprowadzania testów podatności wstępnej i podatności własnej. Na rysunku 2 pokazano kształt przebiegu prądu ESD symulatora według IEC 61000-4-2.

Metoda projektowania układu elektronicznego czy podsystemu lub systemu, powinna obejmować symulacyjne sprawdzanie odporności na ESD zarówno systemu, jak i układu (w ramach oprogramowania EDA). Niestety takie sposoby symulacji są rzadko udostępniane projektantom. Odporność na ESD nie jest dobrze zdefiniowana z uwagi na specyficzne ograniczenia parametrów w symulacjach funkcjonowania i taktowania dla układów cyfrowych lub uwzględniania tętnień zasilania.

A na przykład rodzaje cykli i szybkości interfejsów układów cyfrowych są zdefiniowane dobrze. Ale liczba kombinacji możliwych lokalizacji, amplitud, kształtów i powtarzalności wyładowań ESD z konfiguracją połączeń oraz aktualnie działających funkcji jest nieograniczona. Jeśli zatem magistrala z wystarczającym marginesem spełnia specyfikację czasu setup-and-hold, powinna działać. Jeżeli system wytrzyma test na ESD do 1 kV i do 6 kV, niekoniecznie przejdzie test do 2,5 kV przy tym samym wektorze wejściowym. Gdy wreszcie zespół zapewnienia jakości przetestuje system i wyznaczy jego poziom kwalifikacyjny według przyjętego zespołu kryteriów, to swój werdykt ograniczy tylko do stwierdzenia "przeszedł" albo "przepadł".

Jeśli test jest negatywny

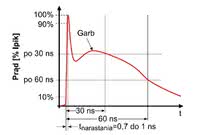

Rys. 2. Symulatory wytwarzają impulsy ESD o przebiegu z garbkiem, zgodnym z IEC61000-4-2, o czasie narastania od 0,7 do 1 ns

Jeśli układ lub system nie zdał testu na wytrzymałość na ESD, konieczne jest wykrycie przyczyn. Istnieje wiele narzędzi do analizy awarii w układach, ale normy i testery systemów nie wskazują przyczyn defektów ani sposobów zapobiegania ich powtórzeniom. Jeśli nawet układ pozytywnie przejdzie przez testy na wymaganym poziomie kwalifikacji (wyniki zwykle są podawane w kilowoltach), nie będzie wiadomo z jakim marginesem zostało dokonane przejście "nad garbkiem".

Odbiorcy niestety nie są zobowiązani do respektowania standardowych kształtów i poziomów impulsów testujących odporność na ESD. Wydaje się, że istnieją nawet użytkownicy lubiący psuć układy. Niektórzy producenci kontraktowi potrafią dokonywać zwrotów produktów motywowanych niepowodzeniem. Wątpliwości powinny być rozwiązywane w warunkach produkcyjnych za pomocą odpowiedniej kontroli ESD w wytwórni, ale przeważnie to projektant musi wykazać, że wina nie leży po jego stronie.

Często projektant systemu musi zidentyfikować zniszczony podzespół i odesłać go producentowi z żądaniem analizy przyczyny uszkodzenia. Natomiast producent elementu może potwierdzić, że przyczyną uszkodzenia jest ESD albo wrzucić tę przyczynę do wspólnego worka "nieznanych przeciążeń elektrycznych". A wtedy na projektanta spada trud uporania się z problemem. Niestety niewiele można zrobić dla zmniejszenia destrukcyjnych tendencji użytkownika.

Zakres narzędzi, porad i wskazówek do analizy przyczyn uszkodzeń wywoływanych przez ESD i do zapobiegania im poszerzył się ostatnio znacznie. Najnowszy sposób testowania odporności na ESD, którym jest skanowanie wewnętrzne, dostarcza dokładniejszych informacji, wprowadza bowiem testowanie do wnętrza układów scalonych.

Wewnętrzne skanowanie

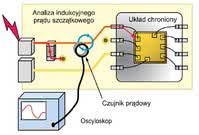

Rys. 3. Systemy skanowania (np. firmy Amber PI) pomagają ustalić ścieżki przepływu prądu ESD, ale wymagają bezpośredniego dostępu do elementów na płytce drukowanej. Skutkuje to jednak utratą integralności ekranowania w trakcie testu

Główne trudności metod testowania odporności na ESD sprowadzają się do problemów z dostępem do układów. W celu umożliwienia przeprowadzenia tradycyjnego skanowania system musi zostać częściowo zdemontowany (rys. 3). Gdy telefon komórkowy czy laptop zostanie otwarty i umieszczony w stanowisku testowania, jego ekranowanie traci skuteczność, a wewnętrzne sprzężenia ulegają zmianom.

Samo wprowadzenie sondy indukcyjnej (rys. 4) może dostarczyć o wiele więcej informacji o tym, gdzie i jak pojawiają się impulsy ESD i jak wprowadzany przez nie ładunek rozchodzi się w systemie. Jest to jednak tylko domniemanie. Istotne są prądy i napięcia w każdym z węzłów systemu, obraz tego, co dokładnie układ odczuwa w momencie wyładowania. Współczesne narzędzia skanujące nie pozwalają precyzyjnie tego zobaczyć.

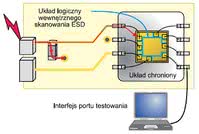

Wewnętrzne skanowanie nowej generacji (rys. 5) dostarcza tych informacji dzięki doprowadzeniu skanowania bezpośrednio do wyprowadzeń we/wy układów. Detektor wbudowany w układzie scalonym może bezpośrednio informować o poziomie i parametrach końcowych w postaci impulsów, które dotarły do wnętrza układu, w kompletnym i działającym systemie.

Obecnie w opracowywaniu jest szereg technik wewnętrznego skanowania. We Francji, w LAAS-CNRS w Tuluzie, zademonstrowano oscyloskop próbkujący 20 GHz, wytworzony w strukturze półprzewodnikowej. Jego zadaniem jest pomiar szczątkowych impulsów ESD, widzianych w układzie scalonym systemu. Obserwacje te mogą posłużyć zarówno do optymalizacji obwodu on-chip, chroniącego przed ESD o aktualnym poziomie mocy, którą musi rozproszyć, jak i do oceny, czy, jak wiele i jakie zewnętrzne obwody osłaniające są potrzebne do pełnej ochrony przed uszkodzeniami.

Na Uniwersytecie Illinois przedstawiono składający się tylko z diody i kondensatora tani i trwały detektor ESD, który może schwytać impuls ESD nawet w niezasilonym urządzeniu, dający się odczytać później. Powstały również wielopoziomowe detektory ESD, nie tak złożone jak LAAS, dostarczające nieco więcej informacji o impulsie. Pojawiła się też prosta technika przerzutników zatrzaskowych, wyzwalanych w komórce we/wy. Monitorowanie przez skanowanie granic JTAG pozwala obserwować "to, co odczuwa układ" poddawany impulsom ESD o rosnącym poziomie. Takie obserwacje pomagają mapować wektory wejściowe i rozładowania w systemie bez konieczności jego demontażu i bez kosztownych urządzeń skanujących.

Oczywiście urządzenie o 400 wyprowadzeniach z oscyloskopem próbkującym na każdym we/wy jest niewykonalne. Ale nawet jednopoziomowo wyzwalany detektor ESD w kilkudziesięciu węzłach systemu może ogromnie poprawić rozumienie tego, co rzeczywiście się dzieje podczas testu kwalifikującego ESD w pełni działającego urządzenia. Operowanie energią ESD on-chip wiąże użytą do tego cenną powierzchnię chipu, co jest bardzo kosztowne, ponieważ mogłaby ona zostać użyta dla ważniejszych obwodów. Zbyt duże zaciski testu ESD zwiększają pojemność pasożytniczą, ograniczającą pasmo interfejsu.

Wewnętrzne skanowanie anty-ESD dostarcza ważnych danych charakteryzacyjnych, które pomagają wypełnić lukę dzielącą projektantów systemu od projektantów podzespołów. Rzeczywiście, gdy technika skanowania jest wprowadzona do podzespołów i udostępnia to cenne narzędzie projektantom, staje się darmowym narzędziem dla zespołów kwalifikujących charakterystyki naprężeń i uszkodzeń w środowisku użytkownika końcowego.

Pozwala nie tylko atestować i debugować uszkodzenia, ale dostarczać długoterminowych informacji statystycznych o aktualnych poziomach obciążenia, napotykanych w różnych aplikacjach i środowiskach geograficznych. Dane takie są niemal niemożliwe do dokładnego uzyskania z danych zmieszanych z "zawieszeniami SO" i innymi efektami przeciążeń elektrycznych, a mogą być bardziej rozważnie i pomysłowo użyte do ustalania poziomów kryteriów i kwalifikacji uszkodzeń, optymalizując czas i koszty zwiększania niezawodności w najbardziej potrzebnych zakresach.

Co dalej?

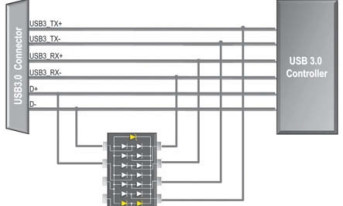

Metody kwalifikacyjne anty-ESD i kontroli fabrycznej są dyscyplinami dojrzałymi i dobrze rozumianymi. Techniki charakteryzacji i analizy powstały w ostatnich latach na skutek gwałtownych potrzeb, wywołanych wzrastającą wrażliwością struktur półprzewodnikowych coraz cieńszych bramek tranzystorów CMOS o niskich napięciach przebicia. Zyskują na znaczeniu te same procesy, które usprawniły Ethernet gigabitowy, interfejsy FireWire, HDMI i USB oraz poszerzyły zakres ich zastosowań na jeszcze trudniejsze mobilne środowiska użytkownika.

Przemysł szybko zbliża się do punktu, w którym narzędzia do analizy ESD nadążą za tymi potrzebami. Mogą one nawet przekroczyć ten trend i pomóc projektantom systemów wyjść poza ślepą metodę prób i błędów przy projektowaniu odporności na ESD.

Jak testowano odporność na ESD?

Rys. 5. Skanowanie wewnętrzne umożliwia przesłanie z wnętrza układu scalonego do komputera obrazu przebiegu impulsu ESD

Pierwsza generacja testów bazowała na wartościach z danych technicznych. Do roku 2005 projektanci systemów działali z zaskakująco wąskimi informacjami od producentów podzespołów o ESD na poziomie systemowym.

Producenci chipów gwarantowali na poziomie układów pewne standardy typu HBM (human-body-model) czy inne, odnoszące się do środowiska obsługi i produkcji. Ale pomiędzy standardami a praktyką powstawała luka, gdyż po wlutowaniu układów w obwody projektanci byli już pozostawiani sami sobie ze swoją wiedzą i doświadczeniem o ESD na poziomie systemu.

Producenci elementów dyskretnych usiłowali tę lukę zapełnić, proponując diody przełączające i Zenera w roli układów TVS (Transient Voltage Suppressor - tłumik przepięć). Producenci ci usiłowali w tym celu testować te układy według standardów poziomu systemowego, jak IEC61000-4-2, których autorzy nigdy takiej konfiguracji nie przewidywali ani nie definiowali. Co gorsza, te układy TVS w sposób nieunikniony były charakteryzowane w takiej konfiguracji, w której nigdy by nie były używane.

Druga generacja - impuls szczątkowy

Zamiast zwyczajnie zająć się napięciowym ograniczaniem TVS czy oceną ESD, projektanci systemów skupili się na redukowaniu prądu szczątkowego (Iszcz), który przedostaje się przez TVS, bazując na Kirchhowskiej zasadzie podziału prądu. Wzajemne oddziaływanie układu testowanego z układem chronionym komplikuje wynik, a 16-kilowoltowy TVS nie może chronić ASIC, bo napięcie progowe diody TVS jest wyższe od napięcia przebicia chronionej bramki tlenkowej. Za przykład może też posłużyć przypadek, gdy dynamiczna rezystancja TVS niewiele się różni od rezystancji wewnętrznej blokady układu chronionego, a prąd impulsu ESD prawie równo dzieli się pomiędzy "odporny" układ testowany i "słaby" układ chroniony.

Zatem druga generacja analizy odporności systemu na ESD ogniskuje się na minimalizacji prądu szczątkowego. Skupiono się na instrumentacji i charakteryzacji Iszcz pomiędzy układem osłaniającym i osłanianym. Niestety jest to czasem trudne w praktyce, ponieważ producenc i układów nie są oczywiście skłonni do ujawniania konkurentom potencjalnych wad swoich wyrobów. Wolą również unikać wyścigu w ochronie przed ESD, aby wyprzedzać konkurencję, nawet jeżeli większość klientów tego nie potrzebuje.

Analizę Iszcz musi przeprowadzać projektant systemu, ponieważ każdy projekt systemu jest unikalnym połączeniem układu chroniącego i chronionego. Producenci półprzewodników nie mogą przewidzieć wszystkich możliwych kombinacji, nie ma więc innego sposobu niż dokładnie przewidująca oddziaływanie symulacja. Projektant systemu musi zatem przecinać ścieżki i prądową sondą mierzyć szczątkowe prądy. A pomiary te będą znaczące dopiero po porównaniu wyników z różnych konfiguracji układów i różnych TVS.

Jest to oczywiście czasochłonne i odrywa od głównego celu, jakim jest równoważenie kosztów z wynikami. Pożądaną opcją byłaby symulacja w programie EDA, ale modele sygnałów układowych (IBIS i in.) ograniczają się do limitowania na poziomie miliamperów, jak w przypadku kilkuwoltowych przepięć, a nie kilowoltowych czy wieloamperowych impulsów, występujących w przeskokach ESD. Modele małych sygnałów nie mogą być ekstrapolowane do takich obrazów dynamicznych rezystancji i punktów przebicia.

Trzecia generacja - skanowanie podatności i rekonstrukcja przebiegów prądowych

Dotychczasowe metody odnosiły się do trwałych uszkodzeń i spalonych elementów. Łatwo dawały się zlokalizować wizualnie lub pomiarami układów scalonych. Miękkie uszkodzenia, które zaledwie zakłócają działanie systemu, ale nie wywołują zniszczeń, są dużo trudniejsze do analizy. Skoncentrowanie się na jednym układzie testującym i pojedynczym we-wy układu sprawdzanego nie musi dokładnie oznaczać sprzężenia, w którym jedna ścieżka jest zaatakowana bez skutków, a pobliska ścieżka zegarowa lub danych uszkodzona.

W takich przypadkach prosty model nie może przybliżyć rzeczywistego zdarzenia. Zdarza się, że przeskok iskry może uszkodzić pobliskie obwody. Trójwymiarowe skanowanie EMI (zakłócenia elektromagnetyczne) urządzenia od dawna stosuje się do wykrywania i identyfikacji nieszczelności w.cz. w chassis układów czy w niespodziewanie zakłócających obwodach elektronicznych. Odwrotnością tego postępowania jest powtarzalne wprowadzanie sygnałów EMI w poszczególne punkty systemu, pozwalające mapować w nim obszary najbardziej podatne na ESD.

Można również wprowadzać sygnały EMI w porty i różne punkty i "odsłuchiwać" je sondą, mapując ścieżki, wzdłuż których się rozładowują. Tego rodzaju skanowanie, rekonstruujące ścieżki prądów ESD, pozwala na szybkie tworzenie obrazu węzłów zagrożonych danym wektorem wejściowym i miejsc rozpraszania się impulsów. Uzyskane rezultaty nie zawsze są zbieżne z przewidywaniami projektanta i stają się pierwszym krokiem na drodze do ustalenia głównego źródła zaburzeń w systemie za pomocą techniki skanowania (rys. 4).

Czwarta generacja - skanowanie wewnętrzne

Dalsza integracja obwodów detekcji obrazowania ESD w układach scalonych obiecuje rozciągnięcie zakresu zrobotyzowanych technik skanowania i równoczesne zmniejszenie kosztów, prowadząc do optymalizacji i poprawy dokładności charakteryzacji. Nawet jeśli jeden z dwóch układów w systemie zawiera detektory zdarzeń ESD z dostępem do sieci skanującej (jak JTAG) systemu, dostępna widzialność z systemu udoskonala wszystkie inne techniki skanowania, symulacji i projektowania.

KKP