Izolacja galwaniczna pomiędzy dwoma punktami obwodu nie pozwala na bezpośredni przepływ prądu elektrycznego pomiędzy nimi, przy czym wciąż możliwy jest transport energii oraz informacji, np. za pomocą sprzężenia pojemnościowego, indukcyjnego lub optycznego. Tego typu izolację powszechnie stosuje się w wielu typach urządzeń, np. w celu ochrony ludzi oraz układów przed wysokim napięciem, zwiększenia odporności na zakłócenia oraz podziału płaszczyzny masy.

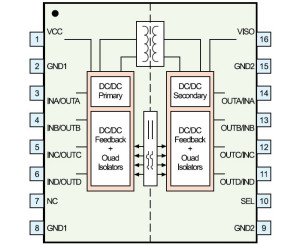

Zazwyczaj konieczne jest jednoczesne zapewnienie izolacji galwanicznej zarówno dla linii zasilania, jak i danych. Izolatory cyfrowe często oferują taką możliwość, co pozwala zaoszczędzić sporo miejsca na płytce drukowanej. Uproszczony schemat blokowy oraz konfigurację wyprowadzeń przykładowego układu tego typu pokazano na rysunku 1.

Wyróżnia się dwa typy izolatorów cyfrowych, ze względu na sposób konstrukcji bariery izolacyjnej - oparte na transformatorach lub na kondensatorach. Izolatory magnetyczne (oparte na transformatorach) są powszechniejsze, zatem to one będą przedmiotem dalszych rozważań.

Wyróżnia się dwa typy izolatorów cyfrowych, ze względu na sposób konstrukcji bariery izolacyjnej - oparte na transformatorach lub na kondensatorach. Izolatory magnetyczne (oparte na transformatorach) są powszechniejsze, zatem to one będą przedmiotem dalszych rozważań.

Transformatory wykorzystywane w tych układach są bardzo małe, składają się niewielkiej liczby zwojów (w celu obniżenia rezystancji uzwojenia) i często pozbawione są rdzenia magnetycznego. Z tego powodu konwerter DC/DC zasilający uzwojenie pierwotne transformatora musi pracować z wysoką częstotliwością, rzędu przynajmniej dziesiątek MHz. Dodatkowo pomiędzy uzwojeniami transformatora istnieje znacznej wartości pojemność pasożytnicza, ponieważ oba uzwojenia znajdują się w niewielkiej odległości od siebie.

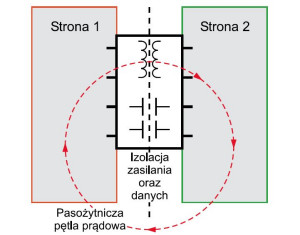

Sygnał o wysokiej częstotliwości przełączania ulega sprzężeniu przez pojemność pasożytniczą, co powoduje przepływ prądu pomiędzy izolowanymi galwanicznie obszarami układu (rys. 2).

Izolacja uniemożliwia bezpośredni przepływ prądów powrotnych, powstaje zatem duża pętla prądowa wykorzystująca pojemności pasożytnicze płytki drukowanej. Finalnie znaczna część energii elektrycznej zostaje wypromieniowana do otoczenia w postaci fali elektromagnetycznej, co skutkuje wzrostem poziomu emisji całego urządzenia.

W przypadku rozwiązań opartych na elementach dyskretnych poziom emisji jest niższy, ponieważ z powodu korzystania z transformatorów o większych rozmiarach (z magnetycznym rdzeniem oraz wyższą wartością indukcyjności) możliwe jest zastosowanie niższej częstotliwości przełączania.

W dalszej części przedstawione zostaną wybrane metody pozwalające obniżyć poziom emisji elektromagnetycznej podczas korzystania z izolatorów cyfrowych.

Wybór odpowiedniego układu

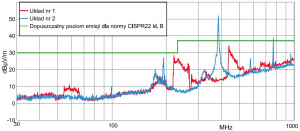

Dostępne na rynku izolatory cyfrowe różnią się pomiędzy sobą pod względem poziomu emisji elektromagnetycznej. Przy wyborze układu warto sprawdzić, czy ma on certyfikaty potwierdzające spełnienie któregoś z obowiązujących w tym zakresie standardów.

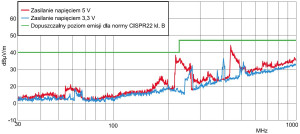

Na rysunku 3 przedstawiono porównanie widma emisji elektromagnetycznej dwóch układów, z których jeden spełnia wymagania standardu CISPR 22B. Badane układy pracowały w jednakowych warunkach na takiej samej płytce drukowanej.

Obniżenie napięcia zasilania

Rys. 4. Porównanie widma emisji elektromagnetycznej tego samego układu pracującego przy różnym poziomie napięcia wejściowego

Izolatory cyfrowe mogą zazwyczaj pracować w szerokim zakresie napięcia wejściowego (przynajmniej od 3 do 5,5 V), dzięki czemu są kompatybilne zarówno z układami zasilanymi napięciem 3,3, jak i 5 V. Praca z niższym napięciem wejściowym pozwala obniżyć poziom emisji elektromagnetycznej układu - maleje szybkość narastania napięcia wyjściowego (SR, slew rate) konwertera DC/DC zasilającego uzwojenie pierwotne, przez co obniża się poziom zakłóceń wspólnych (common mode) przenikających przez barierę izolacyjną oraz poziom emisji elektromagnetycznej układu.

Na rysunku 4 przedstawiono porównanie widma emisji elektromagnetycznej tego samego izolatora cyfrowego pracującego z dwoma różnymi poziomami napięcia wejściowego: 3,3 oraz 5 V. Obniżenie napięcia pozwoliło zauważalnie zmniejszyć poziom emitowanych zakłóceń.

Odsprzęganie wejść i wyjść układu

Rys. 5. Ograniczanie emisji za pomocą dławików oraz kondensatorów odprzęgających na liniach zasilania układu

Jak już wspomniano, izolatory cyfrowe z powodu niewielkich rozmiarów transformatora muszą pracować z wysoką częstotliwością przełączania. Podczas pracy konwerter DC/DC zasilający uzwojenie generuje zakłócenia prądowe propagujące się po linii zasilania. Zakłócenia te mają składniki nisko- oraz wysokoczęstotliwościowe, związane m.in. z częstotliwością przełączania układu.

W celu minimalizacji negatywnego wpływu generowanych zakłóceń warto stosować kondensatory odsprzęgające na liniach zasilania. Jak pokazano na rysunku 5, dobrym rozwiązaniem jest umieszczenie w bezpośrednim sąsiedztwie wejść układu zestawu kondensatorów o różnych pojemnościach (np. C1 = 100 nF, C2 = 1 μF, C3 = 10 μF), co pozwoli skutecznie odfiltrować zakłócenia o różnych częstotliwościach.

Bardzo ważne jest, by umieścić te elementy jak najbliżej wejść układu, aby ograniczyć rozmiary pętli masy (oznaczona na rysunku jako pętla nr 1). Ponadto bliżej układu należy umieszczać kondensatory o mniejszej pojemności. Podobny zestaw filtrów warto umieścić również na wyjściu izolatora.

Pomimo obecności zestawu filtrów na linii zasilania mogą pojawiać się dodatkowe zakłócenia, które nie zostaną odfiltrowane (np. pojedyncze piki prądowe o natężeniu od 100 do 500 mA i czasie kilku ms). Do tłumienia i filtracji takich zakłóceń, szczególnie jeśli ścieżka zasilania jest dość długa, wykorzystać można dołączony szeregowo rezystor o niewielkiej wartości (od 1 do 5 Ω) oraz dodatkowy kondensator odsprzęgający o większej pojemności (np. 100 μF).

Ponadto tłumik ferrytowy zapobiegnie dalszej propagacji zakłóceń o wysokiej częstotliwości. Wszystkie te zabiegi pozwolą ograniczyć obszar pętli masy, przez co zmniejszy się poziom niepożądanej emisji elektromagnetycznej urządzenia.

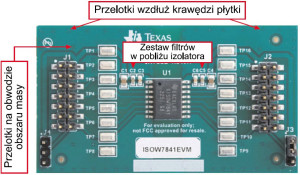

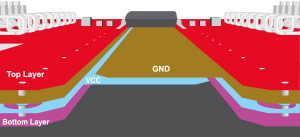

Na rysunku 6 pokazano mozaikę płytki drukowanej, na której umieszczono zestawy kondensatorów odsprzęgających na wejściu oraz wyjściu izolatora cyfrowego. W przedstawionym projekcie zastosowano dodatkowo przelotki rozmieszczone wzdłuż całego obwodu płaszczyzny masy, które łącząc płaszczyzny masy po obu stronach płytki, tworzą klatkę Faradaya. Rozwiązanie takie praktycznie eliminuje emisję elektromagnetyczną z elementów i ścieżek znajdujących się wewnątrz chronionego obszaru.

Wykorzystanie wbudowanego kondensatora

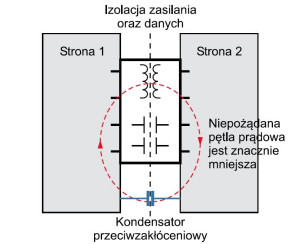

Rys. 7. Kondensator przeciwzakłóceniowy łączący szeregowo izolowane galwanicznie obszary ogranicza rozmiar pętli prądowej

Jednym ze sposobów minimalizacji rozmiarów pętli prądowej obejmującej izolowane galwanicznie obszary płytki (będącej główną przyczyną niepożądanej emisji elektromagnetycznej) jest umieszczenie kondensatora łączącego oba te obszary w bliskim sąsiedztwie izolatora cyfrowego (rys. 7).

Do tego celu najlepiej nadają się kondensatory przeciwzakłóceniowe - najczęściej wykorzystuje się elementy klasy Y2 (napięcie nominalne w zakresie 150-250 V). Niestety kondensator umieszczony na płytce PCB oprócz nominalnej wartości pojemności ma również pasożytniczą indukcyjność (pochodzącą zarówno od samego kondensatora, jak i jego wyprowadzeń), która znacząco ogranicza jego użyteczność w przypadku sygnałów o wyższych częstotliwościach (rzędu kilkuset MHz).

Alternatywnym rozwiązaniem, charakteryzującym się znacznie niższą wartością indukcyjności pasożytniczej, jest uformowanie pojemności bezpośrednio na płytce PCB, z pomocą nakładających się na siebie wewnętrznych warstw płytki.

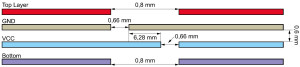

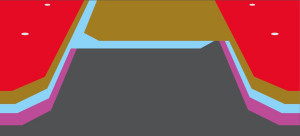

Na rysunku 8 przedstawiono praktyczny sposób realizacji tej koncepcji, na przykładzie płytki czterowarstwowej. Składa się ona z warstwy górnej (warstwa 1), masy (warstwa 2), zasilania (warstwa 3) oraz sygnałowej dolnej (warstwa 4).

Z powodu izolacji galwanicznej warstwy płytki podzielić można na dwie elektrycznie odseparowane grupy, połączone z dwoma różnymi uzwojeniami transformatora. Fragment obszaru warstwy zasilania (VCC1) pierwszej grupy nakłada się na część obszaru warstwy masy drugiej grupy (GND2).

Położone równolegle do siebie warstwy miedzi wraz ze znajdującym się pomiędzy nimi dielektrykiem (laminat FR4) tworzą kondensator płaski.

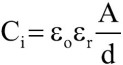

Pojemność tego kondensatora wyraża się wzorem:

|

gdzie εο to przenikalność elektromagnetyczna próżni (8,854 pF/m), εr to względna przenikalność elektromagnetyczna dielektryka (4,2 dla laminatu FR4), A to powierzchnia okładek oraz d - odległość pomiędzy nimi. Przybliżona pojemność kondensatora z rysunku 8 (zgodnie z danymi z tabeli 1) wynosi 30 pF.

Odległości pomiędzy warstwami tworzącymi kondensator (będąca jednocześnie odległością pomiędzy jego okładkami) jest bardzo ważna z powodu konieczności spełnienia wymagań dotyczących izolacji elektrycznej systemu. Minimalna wartość tej odległości określana jest niekiedy w standardach opisujących wymagania dla danej klasy i typu urządzeń.

Podczas projektowania warto wykorzystać minimalną dozwoloną odległość, ponieważ pozwala to na uzyskanie większej pojemności. Przy określaniu odległości koniecznie trzeba jednak uwzględnić również możliwy zakres napięcia na okładkach kondensatora, aby zminimalizować ryzyko przebicia bariery izolacyjnej.

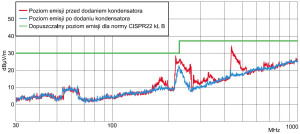

Rys. 10. Emisja elektromagnetyczna układu z izolatorem cyfrowym przed i po dodaniu wbudowanego kondensatora

Przykładowo, dla laminatu FR4 odległość 0,4 mm powinna być wystarczająca dla większości systemów o VRMS poniżej 300 V, zaś 0,6 mm dla systemów o VRMS w zakresie od 300 do 600 V. Warstwa dielektryka powinna być również odporna na działanie chwilowych skoków napięcia o amplitudzie przynajmniej kilkakrotnie przekraczającej wartość nominalną.

Przy tego typu analizie bez wątpienia należy uwzględnić wytrzymałość elektryczną izolatora, która w przypadku laminatu FR4 wynosi ok. 20 kV/mm.

Rysunek 10 obrazuje redukcję emisji elektromagnetycznej uzyskaną po zastosowaniu wbudowanego kondensatora o pojemności 30 pF - taki zabieg pozwolił na obniżenie emisji dla niektórych częstotliwości nawet o ok. 10 dB.

Oprócz określenia odpowiedniej odległości pomiędzy warstwami-okładkami kondensatora, szczególną uwagę należy zwrócić również na wygląd krawędzi płytki PCB w pobliżu kondensatora - różnica napięć powstająca na krawędziach może doprowadzić do odkształceń oraz pęknięć w strukturze płytki. Zaleca się zatem odsunięcie okładek kondensatora od krawędzi płytki oraz wygładzenie kątów na obwodzie poszczególnych warstw (rys. 12).

Bezpośrednie i pojemnościowe połączenie z uziemieniem

Rys. 12. Odsunięcie okładek kondensatora od krawędzi płytki oraz zaokrąglenie krawędzi poszczególnych warstw znacząco zmniejsza ryzyko powstania uszkodzeń płytki

Jeden z obszarów podłączonych do izolatora cyfrowego (tzw. strona kontrolera lub strona "zimna") może być zazwyczaj bezpośrednio podłączony do obudowy (chassis) a przez nią do uziemienia ochronnego. Połączenie takie stwarza możliwość odprowadzenia prądów powrotnych, dzięki czemu ogranicza emisję energii elektromagnetycznej.

Masa obszaru izolowanego może być połączona z uziemieniem za pomocą kondensatora przeciwzakłóceniowego - jest to szczególnie rekomendowane w przypadku interfejsów komunikacyjnych, jak np. RS-485 oraz CAN. Takie pojemnościowe połączenie zapewni ścieżkę powrotną dla różnego typu zakłóceń generowanych w układzie (np. ESD) oraz ograniczy rozmiary niepożądanej pętli prądowej pomiędzy izolowanymi galwanicznie obszarami. Wykorzystanie bezpośredniego i pojemnościowego połączenia układu z uziemieniem przedstawiono na rysunku 13, na przykładzie aplikacji z izolowanym interfejsem RS-485.

Podsumowanie

Rys. 13. Bezpośrednie i pojemnościowe połączenie z uziemieniem w układzie z izolowanym interfejsem RS-485

Wykorzystanie izolatorów cyfrowych znacznie upraszcza konstrukcję urządzenia oraz zmniejsza wymagany rozmiar płytki drukowanej. Specyfika pracy tych elementów może powodować jednak znaczny wzrost niepożądanej emisji elektromagnetycznej całego układu w porównaniu do rozwiązań opartych na elementach dyskretnych.

Bardzo ważna jest zatem znajomość technik pozwalających obniżyć poziom emisji oraz właściwa ich implementacja w opracowywanym projekcie. Do podstawowych zabiegów należy filtracja zakłóceń, wykorzystanie sprzężenia pojemnościowego w celu zapewnienia ścieżki powrotnej dla prądów przepływających pomiędzy izolowanymi galwanicznie obszarami oraz ekranowanie wybranych obszarów.

Damian Tomaszewski