Chociaż 10 przedstawionych w artykule elementarnych reguł projektowania PCB można zalecić zasadniczo do każdego rodzaju urządzeń elektronicznych, to stają się one szczególnie istotne w przypadku urządzeń zawierających szybkie układy i magistrale cyfrowe. Popełnienie nawet pozornie błahego błędu w trasowaniu ścieżek może skończyć się nie tylko pogorszeniem parametrów, ale wręcz uniemożliwieniem prawidłowej pracy urządzenia. Dobrze więc przyswoić sobie omówione zasady i stosować je w praktyce.

1. Ustalenie ograniczeń projektowych

Każde umieszczenie elementu na płytce powinno być poprzedzone dokładnym sprawdzeniem zaleceń projektowych zawartych w odpowiednich notach katalogowych i aplikacyjnych. Wszelkie nieprawidłowości i błędy popełniane na tym etapie skutkują powstawaniem odbić sygnałów, przesłuchów, pojawiają się tłumienia i zakłócenia zasilania (PDN – Power Distribution Networks). Jednym ze stosowanych powszechnie środków zapobiegających takim konsekwencjom są symulacje płytek prowadzone już od wczesnej fazy projektowania. Szczególnego znaczenia nabiera analiza pre-layout pozwalająca definiować krytyczne topologie interfejsów, ustalać optymalne rozłożenie terminatorów szybkich linii cyfrowych, a także dobierać bufory we/wy. Analiza ta powinna być koniecznie wykonywana przed ostatecznym trasowaniem. Na rysunku 1 przedstawiono symulacyjne porównanie przebiegu zegarowego na linii niezaterminowanej (krzywa czerwona) i zaterminowanej (krzywa niebieska).

Choć doświadczony inżynier prawdopodobnie spodziewa się występowania oscylacji na linii bez terminatora, to symulacja pozwala mu ocenić ich wielkość i określić ewentualne zagrożenia. Na wykresie naniesiono wartości progowe dla stanu wysokiego i niskiego, można więc ocenić, czy istnieje niebezpieczeństwo przekraczania tych poziomów.

Etap projektowania pre-layout obejmuje:

- wyznaczanie rezerwowych tras połączeń w celu kontrolowania ich impedancji, zapewnienia integralności sygnału i minimalizacji przesłuchów,

- dobór materiałów dielektrycznych do zastosowań w układach wysokoczęstotliwościowych,

- dobór materiałów pod kątem optymalizacji wydajności produkcji i kontroli kosztów,

- wybór buforów we/wy o odpowiedniej wydajności,

- optymalizację topologii pod kątem integralności sygnału i EMC,

- przyjęcie koncepcji terminowania szeregowego i równoległego,

- rozważenie ograniczeń trasowania związanych z grubościami ścieżek, odstępami między ścieżkami oraz dopasowaniem opóźnień/długości połączeń,

- analizę dystrybucji zasilania (PDN) i optymalizację pojemności odsprzęgających,

- analizę integralności sygnałów pod kątem spełnienia specyfikacji projektowych w odniesieniu do marginesu zaburzeń, timingu, równoczesności zboczy sygnałów synchronicznych, przesłuchów i zniekształceń sygnałów.

Jak widać, projektowanie pre-layout z zastosowaniem zaawansowanych programów symulacyjnych pozwala na wykonywanie minimalnej liczby kroków prowadzących do eliminacji problemów związanych z integralnością sygnałów i zagadnieniami EMC. Dostęp do takich programów jest jednak często ograniczony ze względu na ich duże koszty. Projektanci niedysponujący symulatorami powinni więc bezwzględnie stosować się do zasad projektowania omawianych w artykule, a także zaleceń producentów elementów elektronicznych używanych w projektach.

Jednym z pierwszych etapów projektowania PCB do szybkich układów cyfrowych jest określenie asymetrycznych i różnicowych impedancji linii cyfrowych dla każdej technologii układów scalonych stosowanych w projekcie. Programy używane do projektowania PCB mają zwykle edytory ograniczeń pozwalające na dopasowywanie opóźnień i długości ścieżek magistral, lokalizujące punkty występowania przesłuchów i wskazujące sygnały krytyczne. Sygnały takie uzyskują pierwszeństwo w trasowaniu. Dla ułatwienia pracy projektanta tworzone są grupy i klasy sieci ze zdefiniowanymi dla nich ograniczeniami. Dzięki temu projektant jest na bieżąco informowany o wykonaniu nieodpowiednich działań i związanych z nimi błędach.

Każdy projekt jest inny – to oczywiste. Duża część ograniczeń pozostaje jednak wspólna dla większości projektów, warto więc zdefiniować jeden szablon reguł, który będzie tylko modyfi- kowany w razie potrzeby w konkretnych przypadkach. Na przykład, jeśli w urządzeniu planowane jest użycie interfejsów DDRx, PCIe, USB, SATA, Ethernet, a także mają obowiązywać wspólne ograniczenia produkcyjne, to każdorazowe definiowanie reguł wydaje się niewskazane. Korzystanie ze sprawdzonego szablonu daje ponadto większą gwarancję unikania typowych błędów. Skutkuje to więc mniejszą liczbą błędów wykrywanych później, w kolejnych fazach produkcji. Należy jednak mieć na uwadze, że nawet wielokrotnie stosowany szablon reguł nie zapewnia stuprocentowej poprawności projektu.

2. Kontrolowanie impedancji

Poprawna propagacja sygnałów cyfrowych przez szybkie magistrale jest możliwa tylko w przypadku dopasowania impedancji linii przesyłowej do impedancji nadajnika i obciążenia. Dopasowanie polega na odpowiednim dobraniu rezystorów terminujących. Przy założeniu, że nadajnik współpracuje z obciążeniem wysokoimpedancyjnym, najlepsze warunki transmisji są uzyskiwane wtedy, gdy impedancja linii jest równa impedancji nadajnika. Dobra linia transmisyjna to taka, która ma stałą impedancję na całej swojej długości. Spotykane w technice cyfrowej linie transmisyjne mają impedancję 50...60 Ω. Parametr ten staje się krytyczny dla dużych szybkości przesyłania danych. Należy jednak mieć na uwadze, że różne technologie wymagają określonych impedancji. Są one równe na przykład: 100 Ω dla Ethernetu, 90 Ω dla USB (różnicowo), 50/100 Ω dla DDR2, a dla DDR3/4 to 40/80 Ω (linia asymetryczna/różnicowa). Tak zróżnicowane parametry są sporym wyzwaniem dla projektantów PCB, którzy muszą uwzględniać różne wymagania na jednej płytce. Dodatkowym utrudnieniem jest zmniejszanie się marginesów szumu wraz ze zmniejszaniem napięcia pracy układów. Efekt ten wpływa na zaostrzenie wymagań dotyczących dopasowania impedancyjnego. Ścieżki sygnałowe są ściśle powiązane z płaszczyznami odniesienia chroniącymi przed niepożądanym promieniowaniem występującym szczególnie na zewnętrznych liniach mikropaskowych. Wewnętrzny materiał dielektryczny (między warstwami 5 i 6) jest bardzo cienki, ma grubość 2,3 mils i decyduje o pojemności niskoimpedancyjnych powierzchni rozprowadzających zasilanie.

Niestety, nadajniki nie mają takiej samej impedancji jak linia transmisyjna (zwykle 10...35 Ω), więc do zrównoważenia impedancji i zmniejszenia odbić konieczne jest stosowanie terminatorów. Ale odbicia mogą się też pojawiać, jeśli impedancja linii nie jest stała na całej długości. Przyczyniają się do tego niedopasowane sterowniki/obciążenia, przelotki między warstwami, różne materiały dielektryczne, rozgałęzienia, złącza, obudowy układów scalonych itp.

3. Planowanie rozmieszczenia elementów w oparciu o bazę połączeń

Ta zasada dla doświadczonego konstruktora jest dość oczywista, ale w praktyce bywa trudna do spełnienia ze względu na inne, czasami sprzeczne wymagania. Najogólniej mówiąc, chodzi o to, aby układy o podobnych funkcjach i technologiach wykonania grupować blisko siebie. Przykładem może być oddzielenie części analogowej od cyfrowej, układów szybkich od wolnych itd. W urządzeniu można zwykle wyraźnie wskazać układy agresywne, które będą indukowały przesłuchy w innych układach. Siła oddziaływania jest proporcjonalna do napięcia pracy. Jedną z podstawowych wytycznych w planowaniu rozmieszczenia elementów na PCB jest separacja ze względu na napięcia. Jeśli urządzenie zawiera układy cyfrowe pracujące w logice 3,3 V, a także 1,5 V, należy je w miarę możliwości oddzielać od siebie. Napięcie pracy nie jest jedynym czynnikiem określającym grupy układów, które powinny być separowane. Równie ważnymi parametrami są: czas narastania impulsów i częstotliwość pracy. W celu minimalizowania wpływu szybkich linii cyfrowych na inne układy należy umieszczać je jak najbliżej gniazd i złączy. Rozmieszczanie powinno być dalej stopniowane według malejącej szybkości pracy aż do sekcji analogowej.

Podział na część analogową i cyfrową powinien być zachowany na całej płytce. Oczywiście nie jest to całkowicie możliwe, choćby ze względu na obecność cyfrowych sygnałów sterujących układami analogowymi. Sygnały mogą być segregowane przez stosowanie przegród przebiegających przez wszystkie warstwy płytki. Są to wydzielone obszary płytki, przez które nie może przechodzić żaden sygnał. Takie przegrody można więc zaliczyć do elementów sterowania routingiem (rys. 2).

Należy pamiętać, że szybkie prądy powrotne przebiegają ścieżkami o najmniejszej indukcyjności. Na przykład, jeśli rozpatrzymy połączenie między przetwornikiem DAC a układem FPGA, to droga prądu powrotnego będzie przebiegała bezpośrednio pod ścieżką doprowadzającą sygnał i nie będzie się rozciągać na całą sekcję. Umieszczenie przegród dla sygnałów zapobiegnie wybraniu niepożądanych tras przez autorouter.

Plan rozmieszczenia elementów na płytce musi uwzględniać wspomniane już wcześniej zapewnienie wyrównywania czasów propagacji sygnałów. Decydujące znaczenie ma ścieżka, dla której ten czas jest najdłuższy. Muszą być do niej dostosowane pozostałe ścieżki. Oznacza to, że niektóre z nich muszą mieć sztucznie wydłużoną długość, tak aby w punkcie końcowym nie dochodziło do niedozwolonych opóźnień między zboczami sygnałów. Może się okazać, że niezbędne jest odpowiednie rozsunięcie elementów na płytce. Wszystkie operacje muszą być jednak zgodne z przyjętymi regułami trasowania.

W przykładzie z rysunku 3 przedstawiono wymagane rozmieszczenie elementów i połączenia pomiędzy pamięciami DDR2 i ich sterownikami w topologii typu "T". Projektant powinien dążyć do takiego rozmieszczenia pamięci i sterownika, aby ograniczyć maksymalne długości połączeń. W wielu przypadkach może się to okazać sporym wyzwaniem. Nie jest istotne, które elementy będą umieszczone na górze, które na dole, ważne jest natomiast, aby obszar układów pracujących w logice 1,8 V był odizolowany od pozostałych. Sygnały 1,8 V nie mogą wychodzić poza ten obszar.

4. Określenie płaszczyzn i ścieżek rozprowadzających zasilanie

Rozprowadzenie zasilania po całej płytce obwodu drukowanego jest jednym z trudniejszych zadań. Zasilanie musi dotrzeć do wszystkich elementów aktywnych, nie kolidując przy tym ze ścieżkami sygnałowymi. Do rozprowadzania zasilania wykorzystywanych jest zwykle kilka dostępnych warstw, osobno dla każdego występującego w urządzeniu napięcia. Płaszczyzny zasilania i masy spełniają sześć kluczowych funkcji:

- pozwalają kontrolować impedancję linii zarówno paskowych, jak i mikropaskowych,

- doprowadzają napięcia referencyjne istotne dla wymiany danych cyfrowych,

- rozprowadzają stabilne napięcie zasilania do wszystkich układów logicznych,

- kontrolują przesłuchy między sygnałami przełączanymi,

- zapewniają równomierne rozłożenie pojemności w celu odsprzężenia wysokich częstotliwości,

- stanowią ekranowanie wewnętrznych warstw przed zaburzeniami elektromagnetycznymi.

Coraz większa złożoność współczesnych urządzeń elektronicznych przyczynia się do stosowania wielu napięć zasilających. Pogodzenie wszystkich związanych z tym problemów staje się sporym wyzwaniem dla projektanta. Jedynym możliwym rozwiązaniem, pomimo zwiększenia kosztów, pozostaje użycie płytek wielowarstwowych. Możliwe staje się wówczas osiąganie wymaganej separacji sygnałów krytycznych, a co za tym idzie unikanie przesłuchów i zmniejszanie emisji zaburzeń elektromagnetycznych.

Przykładowa strategia projektowania PCB jest następująca. Po pierwsze, należy zdefiniować obszary zasilania w połączeniu z rozmieszczeniem elementów. Wszystkie elementy powinny być pogrupowane ze względu na realizowane przez nie funkcje z uwzględnieniem wspólnych napięć zasilających. Po drugie, najpierw należy pracować nad obwodami krytycznymi, zapewniając im warstwę uziemiającą z jednej strony i warstwę zasilającą z drugiej. Dzięki temu minimalizowana jest indukcyjność ścieżki prądu powrotnego, zmniejszana jest również powierzchnia pętli. Po trzecie, należy rozdzielać obwody krytyczne za pomocą płaszczyzn uziemienia. Na przykład górne warstwy PCB mogą być wykorzystywane dla jednego obwodu, a dolne dla innego.

Po czwarte, należy unikać nakładania się powierzchni zasilających na pozostałe warstwy, ponieważ sprzężenie między różnymi warstwami zasilania może prowadzić do przenoszenia zaburzeń. Trzeba też starać się w miarę możliwości projektować obszary o kształtach jak najbardziej zbliżonych do kwadratu. Obszary o kształcie prostokątnym mogą generować zaburzenia.

Na rysunku 4 przedstawiono podział obszarów rozprowadzania zasilania. Warto zwrócić uwagę na to, że obwody cyfrowe wykorzystują zwykle to samo uziemienie, nie ma więc powodu do dzielenia płaszczyzn uziemienia. Podzielone płaszczyzny uziemienia tworzyłyby nieciągłość impedancji, stałyby się źródłem powstawania przesłuchów i zaburzeń EMI.

5. Optymalizacja sieci dystrybucji zasilania (PDN)

Ścieżka zasilająca powinna charakteryzować się niską impedancją dla prądu zmiennego. Dąży się do tego, montując na płytce kondensatory obejściowe i odsprzęgające. W PDN występują zarówno pojemności, jak i indukcyjności charakterystyczne dla ścieżek, przepustów, przelotek układów BGA, indukcyjności rozproszenia itd. Częstotliwość rezonansowa obwodu zasilania powinna być kontrolowana w pełnym zakresie, od prądu stałego aż do najwyższej wymaganej częstotliwości, włącznie z harmonicznymi.

PDN musi uwzględniać zmiany prądu przełączania przy możliwie najmniejszych wahaniach napięcia zasilającego (typowo dopuszczalne są 5-procentowe tętnienia). Oznacza to, że impedancja PDN powinna być możliwie jak najniższa w zakresie do maksymalnej częstotliwości występującej w układzie. Wspomniane wcześniej elementy, takie jak ścieżki, przelotki itp., mają specyficzne częstotliwości rezonansowe, dla których impedancja osiąga niskie wartości. Jednak komponenty te oddziałują na siebie, wskutek czego występuje szereg rezonansów, które w katastrofalny sposób mogą wpływać na jakość zasilania. Impedancja docelowa (Ztarget) odpowiadająca wymaganej jakości zasilania jest określana na podstawie najgorszego przypadku zmian prądu i specyfikacji dotyczącej zaburzeń napięcia zasilającego. Jest to maksymalna dopuszczalna impedancja obwodu zasilania i stanowi najważniejszy parametr przy ocenie wydajności PDN. Im bardziej impedancja PDN przewyższa impedancję docelową, tym większe jest prawdopodobieństwo przekłamań podczas pracy urządzenia, a nawet całkowitego jego uszkodzenia.

Kondensatory obejściowe i odsprzęgające są umieszczane w obrębie PDN w celu obniżenia impedancji dla określonych częstotliwości (rys. 5). Kondensatory te osiągają minimalną impedancję dla częstotliwości rezonansowej określonej przez pojemność, równoważną rezystancję szeregową (ESR) i równoważną indukcyjność szeregową (ESL), należy również uwzględniać indukcyjność montażową. Osiągnięcie impedancji docelowej uzyskuje się przez dobranie takiej pojemności, aby po zamontowaniu na płytce drukowanej rezonowała na pożądanej częstotliwości i miała impedancję równą jej ESR. Następnie łączy się równolegle odpowiednią liczbę takich kondensatorów po to, by ich wypadkowa ESR zbliżyła się do pożądanej impedancji docelowej. Każdy dodany kondensator powoduje obniżenie częstotliwości rezonansowej. Można więc założyć, że przez umieszczenie wielu kondensatorów na płytce zostanie pokryty cały zakres częstotliwości. Tym samym impedancja docelowa osiągnie minimalną wartość w zakresie od DC do częstotliwości maksymalnej. Są to jednak rozważania teoretyczne, które w praktyce są bardzo trudne do osiągnięcia. Kondensatory odsprzęgające pracują prawidłowo do częstotliwości ok. 200 MHz. Powyżej istotną rolę w zmniejszaniu impedancji PDN odgrywają przede wszystkim pojemności powierzchni przewodzących.

6. Trasowanie z priorytetem dla sygnałów krytycznych

Zgodnie z tą zasadą sygnały zegarowe powinny zawsze mieć największe opóźnienie w grupie. Połączenia różnicowe powinny utrzymywać stałą impedancję na całej długości. W całym procesie routingu należy przestrzegać przyjętych ograniczeń. Wynikają one z symulacji pre-layout oraz z wymagań i wskazówek producentów podzespołów elektronicznych. Powyższe ograniczenia są ujmowane w regułach projektowania (DRC) i dzięki nim projektant jest na bieżąco ostrzegany o naruszaniu ograniczeń.

Proces routingu powinien przebiegać ze stałym wglądem w schemat ideowy. Najlepiej, gdy są do tego wykorzystywane dwa monitory. Na jednym jest wyświetlany schemat, na drugim edytor PCB.

Na wielowarstwowych płytkach drukowanych sygnały krytyczne powinny być wykonywane jako linie paskowe na warstwach wewnętrznych w otoczeniu stałych płaszczyzn odniesienia (rys. 6). W celu uzyskania jak największego sprzężenia odstęp między ścieżką sygnałową a płaszczyzną powrotną powinien być jak najmniejszy. Przydzielenie tej samej płaszczyzny odniesienia dla sygnału powrotnego (GND, jeśli to możliwe) powoduje zmniejszenie obszaru pętli i redukcję promieniowania zaburzeń.

Na rysunku 7 przedstawiono porównanie emisji zaburzeń promieniowanych przez dwie różne płytki. Na pierwszej ścieżki sygnałowe rozmieszczono na warstwie zewnętrznej, na drugiej te same ścieżki umieszczono na trzeciej warstwie wewnętrznej. W drugim przypadku uzyskano redukcję zaburzeń od 4 do 10 dB. Warto zwrócić uwagę na to, że poziom zaburzeń w pierwszym przypadku przekracza 40 dB. Łatwo można też zauważyć, że składowe widma o wyższych częstotliwościach mają wyższe poziomy. Składowe te mają krótsze długości fali, które stają się porównywalne z długościami ścieżek działających jak anteny. Mimo, że amplitudy harmonicznych maleją wraz ze wzrostem częstotliwości, generowane przez nie zaburzenia pozostają na dużych poziomach zależnych od kształtu ścieżek.

Dla idealnie zrównoważonego sygnału różnicowego zaburzenia emitowane przez jedną linię są kompensowane przez drugą linię. Sygnał wspólny jest jednak średnią z obu linii. Zakładając, że obie linie emitują takie same zaburzenia, nie kompensują się one dla sygnału wspólnego, lecz wzmacniają. Przejście z trybu różnicowego do wspólnego zachodzi na zakrętach ścieżek, niesymetrycznym trasowaniu, w pobliżu przelotek, kołków itp., co ma wpływ na impedancję pary. Dążąc do minimalizacji emisji zaburzeń i przesłuchów, należy mieć na uwadze wszystkie czynniki wpływające na składową wspólną sygnału różnicowego. Można przypuszczać, że główną przyczyną nierównowagi są przesunięcia czasowe między dwiema ścieżkami.

7. Analiza ścieżki powrotnej

Wszystkie ścieżki sygnałowe powinny być ściśle powiązane z płaszczyznami odniesienia. Powinna być dla nich jasno określona ścieżka prądu powrotnego o minimalnej indukcyjności.

Projektanci starają się bardzo precyzyjnie trasować ścieżki sygnałowe, ale często nie przywiązują większej wagi do ścieżek powrotnych. Istotnym zagadnieniem jest zapewnienie tego samego czasu przepływu prądu powrotnego co sygnału. Zwykle przekłada się to na dobranie równych długości ścieżki powrotnej i sygnałowej. Jeśli się o to nie zadba, powstają niepożądane przesunięcia względem sygnału zegarowego. Nieciągłości ścieżki powrotnej mogą być przyczyną powstawania dużych pętli zwiększających indukcyjność szeregową, obniżających integralność sygnału, zwiększających przesłuch i emisję zaburzeń elektromagnetycznych.

Nie można też pomijać drobnych nieciągłości wynikających ze stosowania przelotek i nierównomiernych ścieżek powrotnych dla magistral. Wpływają one na zmianę miejscowych indukcyjności i pojemności ścieżek, stają się ważnym czynnikiem wpływającym na integralność sygnałów.

Każda warstwa sygnałowa powinna być powiązana z płaszczyzną odniesienia stanowiącą dla niej ścieżkę powrotną. Wraz ze zrostem liczby warstw na płytkach drukowanych koncepcja ta staje się łatwiejsza do realizacji, dobór ścieżek powrotnych pozostaje jednak nadal sporym wyzwaniem dla projektanta.

Jakkolwiek płaszczyzny zasilające mogą być wykorzystywane jako płaszczyzny odniesienia, to uziemienie jest bardziej skuteczne, ponieważ lokalne przelotki mogą być używane do realizacji przejść prądu powrotnego zamiast stosowania kondensatorów odsprzęgających. Każdy taki kondensator będzie dodawał również pewną indukcyjność. Dostępność płytek drukowanych o dużej liczbie warstw ułatwia projektantowi pracę, gdyż zwiększa się liczba kombinacji wyboru płaszczyzn.

Niestety, nieciągłości ścieżek powrotnych nie da się wyeliminować całkowicie, można jedynie podejmować kroki minimalizujące ich wpływ. Jak w większości przypadków, należy dążyć do minimalizowania wszelkich pętli.

8. Symulacja post-layout

Gdy płytka została już całkowicie zaprojektowana, pozostało sprawdzenie poprawności jej działania. Jako pierwsza jest stosowana symulacja post- -layot. Sprawdzeniu podlegają sygnały krytyczne. Na tym etapie można jeszcze dokonać korekty propagacji i synchronizacji sygnałów. Symulacja post-layout obejmuje sprawdzenie dzwonienia i jittera.

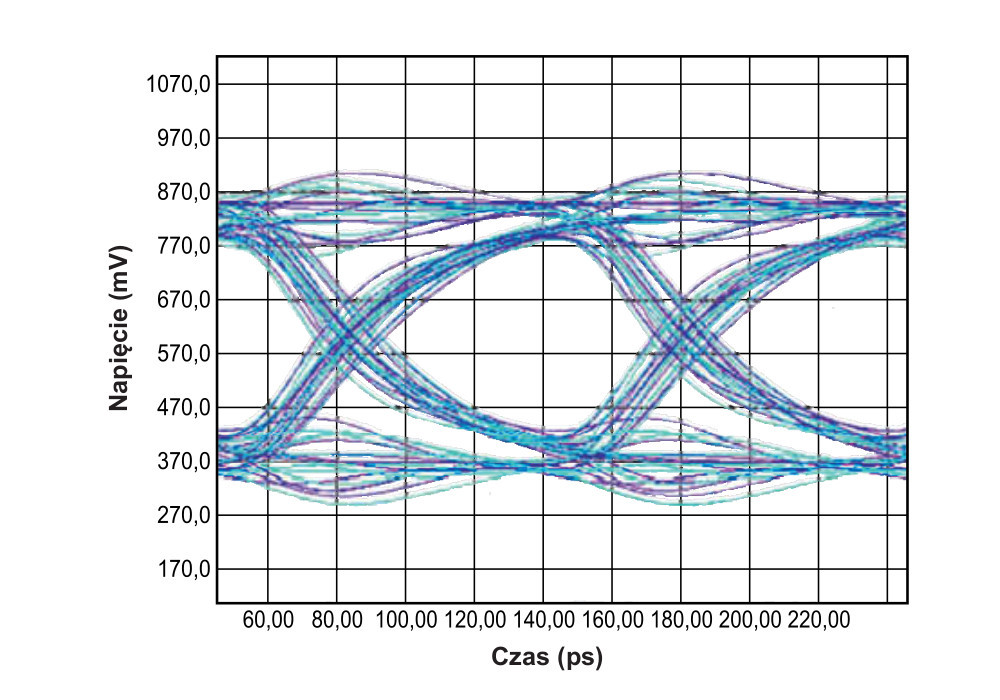

Jedną z częściej stosowanych metod pomiaru jakości szybkich sygnałów cyfrowych jest diagram oka (rys. 8). Na skutek nieidealnych parametrów toru przesyłającego szybkie sygnały cyfrowe na diagramie oka ukazują się nałożone na siebie, ale niepokrywające się przejścia. Uwidaczniają się zarówno niedoskonałości związane z czasem i poziomami sygnału. Tworzą one obraz przypominający oko. Obserwowane niedoskonałości wynikają z mniej lub bardziej konsekwentnego pilnowania omawianych wcześniej reguł i ograniczeń dotyczących projektowania PCB. Symulator sprawdza zgodność uzyskiwanych wyników z wymaganiami związanymi z dopuszczalnymi zaburzeniami EMC, FCC lub CISPR Class A i B. W wyniku symulowanego skanowania płytki sprawdzana jest integralność sygnałów i przesłuchy, a także wskazywane są potencjalne punkty emisji zaburzeń EMC.

Należy pamiętać, że wszelkie problemy związane z integralnością sygnałów są przyczyną nadmiernych przesłuchów, a także powodują powstawanie punktów emisji zaburzeń EMI. Każdy taki punkt powinien być rozpatrywany indywidualnie w celu rozwiązania problemu.

W ramach symulacji post-layout powinny być dokładnie sprawdzone czasy propagacji poszczególnych sygnałów. Są one zależne od meandrowania ścieżek i razie wystąpienia przesunięć czasowych wybrane ścieżki sygnałowe powinny być odpowiednio skorygowane.

9. Eliminacja przesłuchów

Jednym z zadań końcowej symulacji jest wykrywanie ewentualnych przesłuchów. Przesłuchy mogą występować między ścieżkami leżącymi na tej samej warstwie lub między ścieżkami różnych warstw. Przyczyną przesłuchów jest wzajemne oddziaływanie pól elektromagnetycznych. Pole elektryczne poprzez sprzężenie pojemnościowe powoduje pojawianie się napięcia pochodzącego z sygnałów przesyłanych ścieżkami sąsiadującymi. Sprzężenia pojemnościowe wywołują impulsy prądowe generujące odbicia na liniach sygnałowych. Pola magnetyczne natomiast indukują impulsy prądowe na ścieżkach sąsiednich powodujące pojawienie się szumu zasilania.

Siła oddziaływania na siebie dwóch ścieżek maleje proporcjonalnie do kwadratu odległości między nimi. Warto o tym pamiętać. Nawet minimalna korekta przebiegu ścieżek może powodować zauważalne zmniejszenie zaburzeń. Mając na uwadze, że oddziaływanie zachodzi między warstwami płytki można uznać, że ma ono charakter trójwymiarowy.

Dobrą praktyką projektowania jest wzajemnie prostopadłe prowadzenie ścieżek położonych na sąsiednich warstwach. W ten sposób uzyskuje się zmniejszenie obszarów sprzęgania. Jeszcze lepszym rozwiązaniem jest oddzielanie warstw ze ścieżkami warstwami zawierającymi płaszczyznę miedzi.

Projektant przeprowadzając routing interaktywny stara się przestrzegać reguł trasowania, ale zazwyczaj dba również o względy estetyczne. Niestety, nie zawsze są one zgodne z omawianymi zasadami. Zalecane jest, aby – jeśli to możliwe – odległości między ścieżkami krytycznymi nie były mniejsze niż trzykrotna ich szerokość. Odstępstwa od tej reguły są dopuszczalne jedynie w przypadku brakującego miejsca na płytce.

10. Ocena kompatybilności elektromagnetycznej (EMC)

Każdy projektant PCB musi na którymś etapie prac nad płytką zmierzyć się z zagadnieniami EMC. Lepiej myśleć o nich już we wstępnych fazach projektu niż walczyć z niewidzialnym wrogiem na etapie prototypu, nie mówiąc już o produkcji. Niestety na zachowanie kompatybilności elektromagnetycznej wpływa bardzo dużo czynników. Nie zawsze jest możliwe takie zaprojektowanie płytki, aby spełniała ostre normy EMC. Często więc są stosowane dodatkowe elementy ekranujące, zmniejszające emisję EMI i chroniące układ przed polami zewnętrznymi.

Zakładając, że ekranowanie i inne podobne zabiegi powinny być traktowane jako środki ostateczne, zasadne staje się zalecenie, aby identyfikację problemów EMC koncentrować na etapie projektu PCB. Istotnym zagadnieniem staje się identyfikacja tych segmentów połączeń, które mogą być potencjalnym źródłem zaburzeń. W następnym kroku należy podejmować działania mające na celu ich minimalizację. Często dodawane są na przykład dławiki i koraliki ferrytowe, których zadaniem jest ograniczanie wpływu prądów wspólnych (common mode).

Ścieżki przenoszące szybkie sygnały powinny być sprawdzane na etapie symulacji pod kątem wnoszonych przez nie zaburzeń. Norma FCC class B ogranicza średni poziom emisji do 54 dB, dopuszczając (w odległości 3 metrów) szczytowe zaburzenia na poziomie 74 dB powyżej 1 GHz. Niemniej, należy mieć na uwadze, że nieprzewidziane problemy mogą być powodowane również harmonicznymi (rys. 9). Generalnie, źródłem największych zaburzeń są ścieżki położone na zewnętrznych warstwach obwodu drukowanego (linie mikropaskowe). Generują one znacznie większe zaburzenia niż ścieżki umieszczone na warstwach wewnętrznych (linie paskowe). Ukrycie krytycznych ścieżek między płaszczyznami miedzi może zredukować EMI nawet więcej niż o 10 dB.

Zaburzenia elektromagnetyczne emitowane przez pary różnicowe występują jako wspólne lub różnicowe. Zaburzenia różnicowe zwykle kompensują się wzajemnie (przy zachowaniu symetrii pary różnicowej). Zaburzenia wspólne ulegają natomiast wzmocnieniu, gdyż promieniowania wnoszone przez obie linie są takie same. Każda pojemność pasożytnicza lub jakakolwiek niesymetria linii powodowana na przykład opóźnieniami sygnałów synchronicznych, nierównymi czasami narastania i opadania, itp. powodują, że wzrasta znaczenie emisji zaburzeń wspólnych. Także przelotki, bez których niemożliwe jest zaprojektowanie wielowarstwowych PCB zniekształcają sygnały i ograniczają ich pasmo. Stanowią one swego rodzaju anteny o częstotliwości rezonansowej zależnej od głębokości przelotki. Typową metodą rozwiązywania tego problemu jest kontrolowanie głębokości wiercenia, ale tu już bardzo głęboko wchodzimy w proces produkcji obwodów drukowanych.

Zasada 0

Ostatnia zasada jest dopełnieniem wszystkich poprzednich. Trudno ją jednoznacznie sformułować. Konstruktor musi mieć świadomość tego, że nawet najlepsze narzędzia wspomagające projektowanie PCB nie rozwiążą problemu całkowicie i optymalnie. Musi mieć kontrolę na każdym etapie projektu i w razie konieczności wprowadzać ręczne korekty. Nie jest to zadanie łatwe, przysparza ono wielu problemów nawet doświadczonym inżynierom. Można nawet zaryzykować twierdzenie, że do tej pracy potrzebne są specjalne predyspozycje, takie jak:

- dobra komunikacja i współpraca z członkami zespołu,

- zdolność do rozwiązywania trudnych problemów,

- kreatywność, dokładność, staranność,

- znajomość standardów projektowania IPC i specyficznych wymagań projektu,

- dokładna znajomość narzędzi EDA oraz procesów wytwarzania PCB, ich montażu i testowania,

- znajomość zjawisk związanych z propagacją sygnału w liniach transmisyjnych, umiejętność kontrolowania impedancji, rozpoznawania dróg przepływu prądu oraz lokalizowania sprzężeń dla wysokich częstotliwości

- zadowolenie z pracy i entuzjastyczne podchodzenie do kolejnych wyzwań.

Jarosław Doliński