Chiang dodał, że przeszkodą we wprowadzeniu tych technologii mogą być dostawcy narzędzi produkcyjnych. Firma planuje uruchomienie pilotażowej linii 450nm w zakładzie Fab 12 w Hsinchu, po czym produkcja miałaby być rozpoczęta w kompleksie Taichung.

Według TSMC wprowadzenie wymiaru płytek o średnicy 450mm pozwoliłoby zmniejszyć koszt wytwarzania o 30%, ponieważ produkcja mogłaby być wykonana w mniejszej liczbie fabryk, a więc na mniejszej powierzchni i przy mniejszych kosztach pracy.

Na poparcie tej tezy firma przedstawiła następujące wyliczenie: przy zamówieniu chipów o wielkości 32 mln płytek 200mm, gdyby TSMC zastosował płytki 450-milimetrowe, musiałby zatrudnić 20 tysięcy inżynierów w 22 fabrykach. Do wykonania takiego zamówienia na płytkach 300-milimetrowych tajwańska wytwórnia potrzebuje 27 tysięcy inżynierów i aż 29 fabryk.

Problemy z litografią EUV

Kalkulacja ta nie oznacza, że szybko zapadną decyzję o przejściu na płytki 450mm. TSMC przekazał dostawcom sprzętu fabrycznego własne uwagi i specyfikacje dotyczące nowego standardu wielkości płytek, jednak nie wywołały one entuzjazmu u wszystkich dostawców. Do wykonania narzędzi zrażają bowiem ich dostawców wysokie koszty i to zarówno jeśli chodzi o płytki o większej średnicy, jak i skanery do litografii.

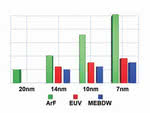

Standardowa wydajność fabryk półprzewodników wynosi co najmniej sto płytek na godzinę dla jednego systemu produkcyjnego. Jak na razie jednak zastosowanie obecnych skanerów do litografii w ekstremalnie dalekim ultrafiolecie (EUV) daje wydajność pojedynczej maszyny najwyżej pięciu płytek krzemowych na godzinę. A alternatywna technologia litografii z użyciem wiązek elektronowych (multiple e-beam direct write) umożliwia produkcję w ciągu godziny niecałej jednej płytki.

Rys. 1. Wzrost kosztów produkcji płytek półprzewodnikowych dla procesów poniżej 28nm (ArF – litografi a immersyjna, EUV – litografi a EUV, MEBDW – litografi a wiązką elektronową); źródło: TSMC

Obecnie stosowane skanery do litografii immersyjnej 193nm będą używane zarówno w procesie 28nm, w którym TSMC wciąż rozwija i zwiększa produkcję, jak w procesie 20nm następnej generacji. Przy rozmiarze charakterystycznym 20nm konieczne jest stosowanie tzw. double patterning, tj. wykonanie pewnych procesów naświetlania na płytce dwukrotnie, aby uzyskać bardziej gęste rozmieszczenie linii.

Przy technologii 14nm liczba dwukrotnych naświetleń na płytce za pomocą skanerów immersyjnych wzrosłaby jeszcze bardziej, powodując zaporowo wysokie koszty dla części klientów. W związku z tym TSMC testuje prototypowy skaner EUV serii 3100 dostarczony przez ASML.

Jeszcze wcześniej TSMC rozpoczął testowanie skanera e-beam od Mapper Lithography i przymierza się do instalacji kolejnego urządzenia e-beam, firmy KLA Tencor.

Według firmy kluczowe jest jednak uzyskanie skanerów typu EUV lub e-beam o wydajności co najmniej 100 płytek na godzinę, aby klientom opłacało się wdrażać nową technologię. Z kolei dalsze wytwarzanie chipów w litografii immersyjnej jeszcze bardziej utrudni przejście na EUV w przyszłości. Jednocześnie zasady projektowania układów scalonych zależą od wyboru typu litografii, dlatego TSMC, chcąc jak najszybciej ustalić termin, proponuje ruszyć z procesem 14nm od 2015 r.

Marcin Tronowicz