W zestawieniu z innymi metodami pakowania technologia fan-out ma wiele zalet. Najważniejsze z nich to: mniejsze rozmiary oraz lżejsza konstrukcja, możliwość upakowania w obudowie większej liczby elementów w pionie, krótsze wyprowadzenia (mniejszy wpływ parametrów pasożytniczych, mniejsze opóźnienia sygnałów), mniejszy pobór prądu oraz mniejsza rezystancja termiczna.

Początki FOWLP

W centrum zainteresowania obudowy FOWLP są mniej więcej od dwóch lat. Prace nad nimi trwają jednak znacznie dłużej - początki historii technologii fan-out sięgają końca 2007 roku.

Wówczas firma Infineon zaczęła rozwijać pierwszą technologię pakowania, którą można zaliczyć do tej grupy. Były to obudowy typu eWLAB (Embedded Wafer-Level Ball Grid Array).

Następnie prace nad nimi, wspólnie z tym producentem, kontynuowały firmy STMicroelectronics i STATS ChipPAC. Początkowo kooperacja ta miała charakter nieformalny. Jednak w 2008 roku przedsiębiorstwa te sformalizowały ją, zakładając stowarzyszenie, którego celem było dalsze rozwijanie tej metody pakowania.

Rok później firmie Infineon udało się jako pierwszej skomercjalizować własną wersję technologii obudów eWLAB. Została ona wdrożona w podzespołach w telefonach komórkowych marki LG.

Rozwój

Poza tym od 2010 roku układy wyprodukowane w tej technologii są częścią telefonów Nokii. Na przełomie lat 2009 i 2010 produkcję na masową skalę układów nadawczo-odbiorczych do telefonów komórkowych w obudowach FOWLP rozpoczął Intel Mobile.

W 2013 roku swoje podejście do technologii fan-out zaprezentowała też firma Deca Technologies. Z kolei rok później utworzono konsorcjum High Density Fan-Out Wafer-Level Packaging, na czele którego stanęła singapurska instytucja naukowa A*Star IME (Agency for Science, Technology and Research Institute of Microelectronics). Wśród członków tego stowarzyszenia znalazły się m.in. firmy: Amkor, Nanium, STATS, NXP, Applied Materials, GlobalFoundries, K&S, Dispol, Kingyoup, JSR, KLA-Tencor, Orbotech oraz TOK.

| Rys. 1. Porównanie technologii typu fan-in (u góry) i typu fan-out (u dołu) | Rys. 2. Różne wersje technologii InFO |

Przełom

W 2016 roku A*Star IME powołało kolejną tego typu jednostkę badawczo-rozwojową. Było to Multi-chip Fan-Out Wafer Level Packaging Development Line Consortium (FOWLP DLC).

Prawdziwy przełom nastąpił jednak dopiero wtedy, gdy w 2016 roku układy w obudowach w technologii InFO (Integrated Fan-Out), opracowanej przez firmę TSMC, a konkretnie procesory aplikacyjne A10, zostały wykorzystane przez Apple w iPhone’ach 7.

Ściślej, procesory A10 zostały wykonane w technologii FO PoP (DRAM-on-Processor), w której nad procesorem w obudowie InFo umieszczono pamięci LPDDR4 DRAM firmy Samsung, o pojemności 2 GB w przypadku iPhone’ów 7 i 3 GB w iPhone’ach 7 Plus. Na rysunku 2 zostały przedstawione różne wersje technologii InFO rozwijanej przez TSMC.

Stan obecny

Krok ten wzbudził ogromne zainteresowanie obudowami typu fan-out, zobrazował bowiem wszystkim możliwości, jakie drzemią w tej technologii pakowania układów scalonych w przypadku złożonych urządzeń, a zarazem tych produkowanych na masową skalę. Potwierdzenie dużego potencjału technologii FOWLP stanowią też plany firmy Apple, która w 2017 roku ogłosiła, że następna generacja procesorów aplikacyjnych, A11, również zostanie umieszczona w obudowach InFO.

Sytuację na rynku obudów typu fan-out od paru lat obserwuje firma Yole Développement. Według niej można na nim wyróżnić dwa segmenty. Do pierwszego zaliczane są chipy "prostsze", jak na przykład transceivery, natomiast do drugiego te bardziej "skomplikowane", o dużej liczbie I/O, jak procesory oraz pamięci. Według analityków potencjał obu jest równie wysoki, toteż oba będą szybko rosnąć. Napędzać je jednak będą różne czynniki.

Odbiorcy i dostawcy się uzupełniają

Jeżeli chodzi o pierwszy segment, to zainteresowanie spopularyzowaniem technologii pakowania FOWLP w produkcji coraz większej liczby rodzajów układów scalonych, takich jak m.in. kodeki i PMIC (Power Management Integrated Circuits), wykazuje coraz większa liczba liczących się firm, jak na przykład Qualcomm, zaś większość firm z branży OSAT (Outsourced Semiconductor Assembly and Test) jest na to wyzwanie gotowa.

Wynika to z ugruntowanej pozycji tych ostatnich na rynku technologii pakowania FOWLP, którą zawdzięczają temu, że od dłuższego czasu dysponują możliwościami technicznymi w tym zakresie. Przykładami przedsiębiorstw z branży OSAT są m.in.: JCET/STATs ChipPAC, ASE i Amkor. Yole Développement w związku z tym prognozuje w najbliższych latach stały wzrost tego sektora rynku obudów fan-out.

Potrzebni są nowi klienci

W przypadku jego drugiego segmentu jak na razie wyłącznym odbiorcą jest firma Apple, jedynym typem układów umieszczanych w tych obudowach są procesory aplikacyjne, natomiast możliwości techniczne w tym zakresie ma tylko firma TSMC. Według Yole Développement, jeżeli chodzi o to ostatnie, to firmom z branży OSAT może zająć jeszcze wiele lat, nim będą w stanie wejść na ten rynek.

Analitycy przewidują jednak, że jeśli inni odbiorcy, poza Apple, jak na przykład Qualcomm, Huawei czy Samsung, zdecydują się również w przypadku bardziej zaawansowanych układów przestawić się na obudowy typu fan-out, wartość tego sektora w najbliższych latach wzrośnie powyżej 1 mld dolarów. Dla porównania, w 2017 roku oszacowano ją na 500 mln dolarów.

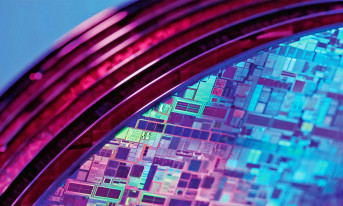

Metoda Fan-out w zamykaniu (pakowaniu) struktur scalonych. O co w tym chodzi?Idea kryjąca się za obudową Fan-out WLP (wafer-level package) jest taka, aby osadzić strukturę półprzewodnikową na dodatkowej cienkiej warstwie epoksydowej zapewniającej rozsunięcie kontaktów na większy obszar. Celem takiego sposobu montażu jest większa integracja, możliwość wyprowadzenia większej liczby połączeń ze struktury, bez konieczności drastycznego zmniejszania rastra między polami kontaktowymi. Liczy się także dobry kontakt cieplny struktury z podłożem. W tradycyjnej obudowie WLP pola kontaktowe są rozłożone na całym spodzie struktury. Im jest ona mniejsza a linii komunikacyjnych więcej, tym większe trudności technologiczne z montażem SMT. Stąd w fan-out strukturę osadza się na tanim podłożu epoksydowym EMC (epoxy mold compound) zawierającym sieć redystrybucji miniaturowych kontaktów wykonanych na krzemie na większą powierzchnię podłoża epoksydowego. Dzięki temu chip może być bez problemu montowany w procesie SMT, a raster wyprowadzeń nie musi być ekstremalnie mały. |

Monika Jaworowska