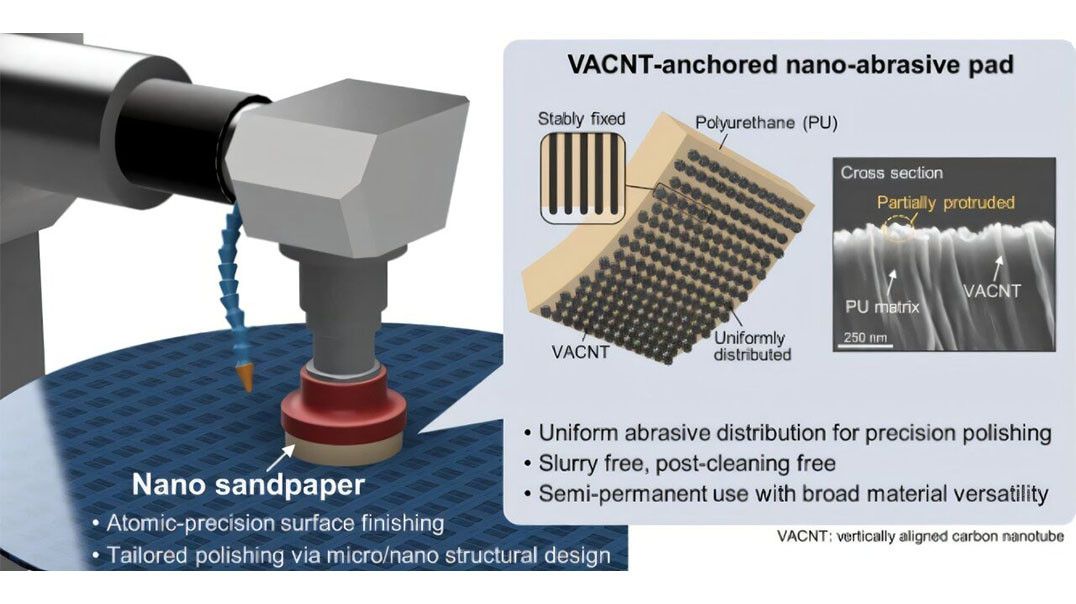

Technologia opracowana w Korea Advanced Institute of Science and Technology (KAIST) przenosi koncepcję klasycznego papieru ściernego do skali nanometrycznej, umożliwiając równomierną i kontrolowaną obróbkę powierzchni półprzewodników. Może ona znaleźć zastosowanie w najbardziej wymagających procesach wytwarzania układów scalonych, gdzie kluczowe znaczenie ma precyzyjna kontrola topografii powierzchni.

Papier ścierny w skali nano

Zespół badawczy pod kierownictwem prof. Sanha Kima z Wydziału Inżynierii Mechanicznej opracował tzw. „nano-papier ścierny”, w którym materiałem ściernym są nanorurki węglowe – struktury nawet kilkadziesiąt tysięcy razy cieńsze od ludzkiego włosa. Technologia ta umożliwia bardziej precyzyjną obróbkę powierzchni niż konwencjonalne procesy produkcji półprzewodników, a jednocześnie ogranicza obciążenie środowiskowe związane z procesem wytwarzania. Stanowi tym samym alternatywną metodę planaryzacji.

Wyniki badań opublikowano w czasopiśmie Advanced Composites and Hybrid Materials w artykule pt. „Carbon nanotube sandpaper for atomic-precision surface finishing”.

Tradycyjny papier ścierny, choć powszechnie stosowany do wygładzania powierzchni poprzez ścieranie, nie znajduje zastosowania w przemyśle półprzewodnikowym ze względu na ekstremalne wymagania dotyczące precyzji. Konwencjonalny papier ścierny powstaje przez przyklejenie ziaren ściernych do podłoża za pomocą spoiwa, co utrudnia równomierne rozmieszczenie bardzo drobnych cząstek i ich stabilne mocowanie.

Aby sprostać tym wymaganiom, przemysł półprzewodnikowy stosuje proces planaryzacji chemiczno-mechanicznej (CMP), w którym wykorzystuje się zawiesinę z rozproszonymi cząstkami ściernymi. Metoda ta wymaga jednak dodatkowych etapów czyszczenia i generuje znaczne ilości odpadów, co zwiększa złożoność procesu oraz jego wpływ na środowisko.

Struktura o ekstremalnej gęstości ziaren ściernych

W odpowiedzi na te ograniczenia zespół badawczy opracował rozwiązanie przenoszące koncepcję papieru ściernego do skali nanometrycznej. Nanorurki węglowe zostały ustawione pionowo, zakotwiczone w matrycy poliuretanowej i częściowo odsłonięte na powierzchni, tworząc strukturę „nano-papieru ściernego”. Takie rozwiązanie konstrukcyjne skutecznie ogranicza odrywanie się elementów ściernych, minimalizuje ryzyko uszkodzenia obrabianej powierzchni oraz zapewnia stabilność parametrów nawet przy wielokrotnym użyciu.

Opracowany materiał charakteryzuje się gęstością ziaren ściernych około 500 000 razy większą niż w przypadku najdrobniejszego komercyjnego papieru ściernego. Precyzję papieru ściernego określa się poprzez tzw. liczbę ziarnistości, która odzwierciedla zagęszczenie cząstek ściernych na powierzchni.

Potwierdzona skuteczność i redukcja defektów

Skuteczność technologii potwierdzono eksperymentalnie. Chropowate powierzchnie miedzi wypolerowano do poziomu gładkości rzędu nanometrów. W testach planaryzacji struktur wzorcowych półprzewodników odnotowano redukcję defektów typu dishing nawet o 67% w porównaniu z konwencjonalnym procesem CMP.

Defekt „dishing” polega na powstawaniu wklęśnięć w centralnej części linii połączeń, co negatywnie wpływa na parametry elektryczne oraz niezawodność zaawansowanych układów, w tym pamięci HBM.

Istotną zaletą nowej technologii jest fakt, że elementy ścierne są trwale zamocowane w strukturze materiału, dzięki czemu nie ma potrzeby ciągłego podawania zawiesiny ściernej, jak w przypadku CMP. Ogranicza to liczbę etapów czyszczenia oraz eliminuje odpadową zawiesinę, otwierając drogę do bardziej przyjaznych środowisku procesów produkcji półprzewodników.

Badacze przewidują możliwość zastosowania technologii w zaawansowanych procesach planaryzacji wykorzystywanych przy produkcji pamięci HBM dla serwerów AI, a także w procesach łączenia hybrydowego, uznawanych za jedną z kluczowych technologii połączeń międzyelementowych w półprzewodnikach nowej generacji.

Nowy kierunek w technologii obróbki powierzchni

Zdaniem zespołu badawczego opracowana metoda znacząco rozszerza klasyczną koncepcję papieru ściernego, wprowadzając ją do obszaru obróbki precyzyjnej w skali nano i wskazując na możliwość pozyskania kluczowych technologii dla przemysłu półprzewodnikowego.

Jak podkreślił prof. Sanha Kim:

- To pionierskie badanie pokazuje, że koncepcję codziennego papieru ściernego można skutecznie rozszerzyć do skali nanometrycznej i zastosować w ultradrobnych procesach produkcji półprzewodników. Mamy nadzieję, że technologia ta przyczyni się nie tylko do poprawy parametrów układów scalonych, ale również do rozwoju bardziej ekologicznych procesów wytwórczych.

Źródło: Phys