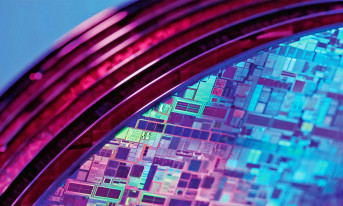

Partnerstwo koncentruje się na rozwoju nowych technik tworzenia wzorów (patterning) oraz technologii połączeń międzywarstwowych. Obecnie najwięksi producenci półprzewodników, w tym firma TSMC, nadal korzystają z technik multi-patterningu oraz starszych systemów Low-NA EUV, wstrzymując się z wdrożeniem maszyn High-NA. Mimo braku implementacji tej technologii TSMC pozostaje liderem produkcji najbardziej zaawansowanych procesów technologicznych dostępnych komercyjnie.

IBM, który w 2021 roku jako pierwszy na świecie zaprezentował układ wykonany w technologii 2 nm, współpracuje obecnie z japońską firmą Rapidus nad rozpoczęciem produkcji w tym procesie już w przyszłym roku. Według przedstawicieli firmy przejście na litografię High-NA EUV jest nieuniknione ze względu na fizyczne ograniczenia dalszej miniaturyzacji.

– Jesteśmy podekscytowani rozszerzeniem naszej współpracy, aby stawić czoła kolejnym wyzwaniom związanym z wdrożeniem litografii High-NA EUV i węzłów sub-1-nm – powiedział Mukesh Khare, dyrektor generalny IBM Semiconductors w IBM Research.

Wyzwania skalowania poniżej 1 nm

Jak podkreślają przedstawiciele Lam Research, dotychczasowe metody produkcji zaczynają osiągać swoje granice w najbardziej zaawansowanych procesach technologicznych. Skalowanie poniżej 1 nm wymaga zupełnie nowych podejść do materiałów, procesów technologicznych i kontroli produkcji.

– Skalowanie wymiarów urządzeń przesuwa granice fizyki, wymagając całkowicie nowych materiałów, technik tworzenia wzorów oraz strategii kontroli procesu na poziomie atomowym. Uzysk produkcyjny (yield) jest w coraz większym stopniu uzależniony od fluktuacji w skali atomowej i interakcji procesowych. To sprawia, że współoptymalizowane, zintegrowane w skali atomowej przepływy osadzania i trawienia stanowią kluczowe wyzwanie dla logiki sub-1-nm. Lam skupi się na umożliwieniu precyzji na poziomie atomowym w tworzeniu wzorów, trawieniu i osadzaniu, tak aby ultracienkie wzory EUV mogły być niezawodnie przenoszone na rzeczywiste warstwy układu przy uzysku na poziomie produkcyjnym – wyjaśnia Vahid Vahedi, dyrektor ds. technologii i zrównoważonego rozwoju w Lam Research.

Vahedi zwrócił również uwagę na ograniczenia obecnie stosowanych systemów litograficznych.

– W przypadku Low-NA te zaawansowane węzły wymagają wielokrotnego naświetlania, co skutkuje wyższymi kosztami, dłuższymi cyklami produkcyjnymi i niższym uzyskiem – podkreślił.

Nowe materiały dla litografii EUV

Lam Research wniesie do współpracy swoje najnowsze technologie tzw. suchych rezystów (dry resist) – nowej klasy materiałów do litografii EUV, w których proces wywoływania wzoru odbywa się w fazie gazowej zamiast w roztworze chemicznym. Technologia ta ma poprawić rozdzielczość oraz ograniczyć defekty, umożliwiając bezpośrednie formowanie wzoru w litografii High-NA EUV, co przekłada się na wyższy uzysk produkcyjny i lepszą jakość odwzorowania struktur.

– Jesteśmy dumni, że możemy opierać się na naszej udanej współpracy z IBM, aby napędzać przełomy w procesach i suchych rezystach dla High-NA EUV, przyspieszając rozwój tranzystorów o niższym poborze mocy i wyższej wydajności, które będą kluczowe dla ery sztucznej inteligencji – dodał Vahedi.

Mukesh Khare z IBM podkreśla, że wdrożenie nowej generacji systemów litograficznych może zdefiniować rozwój branży półprzewodników w nadchodzącej dekadzie.

– IBM wierzy, że przyspieszenie jej wdrożenia umożliwi powstanie wysokowydajnych układów AI potrzebnych w erze sztucznej inteligencji. Osiągnięcie tego celu będzie jednak wymagało postępów w materiałach, procesach trawienia i osadzania, transferze wzorów oraz innych elementach technologii, aby w pełni wykorzystać korzyści kosztowe i wydajnościowe – zaznaczył.

Albany NanoTech jako centrum badań

Badania prowadzone będą w Albany NanoTech Complex w stanie Nowy Jork, gdzie działa pierwsze w Ameryce Północnej publiczno-prywatne centrum badań nad litografią High-NA EUV. Oprócz współpracy z Lam Research i Rapidusem IBM rozwija tam również technologie modelowania odprowadzania ciepła we współpracy z firmą Synopsys oraz przy wsparciu agencji DARPA, z myślą o przyszłych procesach sub-2 nm. Firma utrzymuje także partnerstwo produkcyjne z Samsungiem.

Celem najnowszego porozumienia obu firm jest opracowanie kompletnych przepływów procesowych dla nowych architektur tranzystorów.

– Nasze zespoły dążą do opracowania pełnych przepływów procesów dla urządzeń typu nanosheet i nanostack oraz technologii dostarczania zasilania od tyłu (backside power delivery) – wyjaśnia Khare. – Celem jest umożliwienie niezawodnego przenoszenia wzorów High-NA EUV na warstwy układu przy wysokim uzysku oraz wsparcie dalszego skalowania, poprawy wydajności i realnych ścieżek produkcyjnych dla przyszłych układów logicznych.

Firmy nie ujawniły dotychczas potencjalnych partnerów produkcyjnych (foundry), którzy mieliby odpowiadać za komercyjną produkcję nowych układów, ani harmonogramu ich wdrożenia na rynek.

Źródło: EE Times