Można by próbować prześwietlenia układu promieniami Roentgena, ale uzyskałoby się jedynie statyczny obraz połączeń, a nie dynamiczny obraz elektryczny, potwierdzający działanie. Można by wymienić układ BGA na nowy w nadziei, że to rozwiąże problem. Zwykle jest to kosztowne, czasochłonne i mało skuteczne. Dobrym rozwiązaniem jest przeprowadzenie skanowania ścieżką krawędziową (boundary scan), wykorzystując zawarte w układach scalonych porty JTAG.

Wystarczy nauczyć się, jak z tej możliwości korzystać. Punktem wyjścia jest informacja, czy poszukiwany sygnał jest doprowadzony do któregoś z punktów pod układem BGA. Może to być linia zegarowa, adresowa, magistrala danych itp. Pożądana jest wiedza, czy jego stan jest wysoki, niski, czy zmienia się i w którą stronę i czy kontakt w złączu jest zachowany. Do informacji tych można dotrzeć w sposób nietradycyjny, wykorzystując przystosowanie układu scalonego do skanowania ścieżką krawędziową.

Pomysł jest prosty - układowi scalonemu zleca się rejestrację stanów wszystkich wyprowadzeń, wysyłanie ich na zewnątrz za pośrednictwem rejestru przesuwnego i kolejnego wyświetlania na ekranie komputera. Użytkownik może zobaczyć dynamiczny obraz aktywności wszystkich skanowanych wyprowadzeń BGA, może wymuszać stany logiczne na poszczególnych wyprowadzeniach jednego układu i dokonywać odczytów na innych połączonych z nim wejściach, sprawdzając w ten sposób istnienie połączeń na płytce drukowanej i brak zwarć pomiędzy sygnałami.

Można w ten sposób sprawdzić, czy oscylator jest połączony z odpowiednim wyprowadzeniem lub co się dzieje w magistrali adresowej lub danych - wszystko w czasie rzeczywistym, natychmiast i to bez poruszania płytki. A najlepszą właściwością tej techniki jest to, że układ "nie odczuwa" tych manipulacji, a jego działanie pozostaje całkowicie przejrzyste. Aplikacja może działać z pełną szybkością pomimo monitorowania każdego z wyprowadzeń.

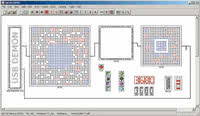

Na rysunku 1 jest pokazany obraz, generowany przez demonstracyjny program narzędziowy J-SCAN firmy MacRaigor Systems, ilustrujący działanie tej techniki. Widać na nim każde wyprowadzenie każdej części łańcucha JTAG. Wszystkie te wyprowadzenia są zakodowane kolorem, pokazującym ich stan wysoki lub niski, a przemiany tych kolorów wykazują jego aktywność. Pozwala on za pomocą kliknięć myszą sterować magistralą adresową czy przerzucać stan linii do złącza lub LED, sprawdzając połączenia.

Oczywiście, gdy testy urządzeń w produkcji realizowane są całkowicie automatycznie. Odpowiednie programy narzędziowe są w stanie wygenerować niezbędne dane do wymuszeń sygnałów i następnie dokonać odczytów na wyjściach, sprawdzając, czy wszystkie połączenia są dobre. Przy dużej liczbie połączeń na płytkach drukowanych jest to jedyna metoda, aby mieć pewność, że wszystkie połączenia są dobre.

Jak z wyprowadzenia układu scalonego przejmować informacje?

Niemal każdy nowoczesny cyfrowy układ scalony ma dzisiaj port JTAG. Jest to po prostu ogromny rejestr przesuwny podłączony przez bufory do wyprowadzeń i układ sterujący jego zachowaniem. Każdy bit w rejestrze odczytuje lub steruje jednym z wyprowadzeń. Podglądanie stanu wyprowadzeń polega na ich przepisaniu do rejestru i przesłaniu je następnie do portu JTAG. Robi się to raz za razem, a wyniki wyświetla na ekranie.

W ten sposób otrzymuje się obraz tego, jaki stan jest na każdym wyprowadzeniu w czasie rzeczywistym. W jednym z takich rejestrów typowego układu FPGA lub procesora jest zwykle 300 do 400 bitów. To, co każdy z bitów rejestru przedstawia, jest zdefiniowane w pliku BSDL (Boundary Scan Description Language). Plik ten można bezpłatnie ściągnąć z witryny producenta danego układu scalonego. Opisuje on dokładnie funkcje każdej komórki łańcucha skanowania krawędziowego i jej powiązania z fizycznymi wyprowadzeniami.

Z pliku BSDL można się zorientować, że zazwyczaj z każdym wyprowadzeniem układu są związane trzy komórki skanowania. Jedna służy do przejmowania sygnałów wejściowych układu i sterowania nimi, druga analogicznie do sygnałów wyjściowych, a trzecia do przejmowania i sterowania zezwoleniem bufora wyjściowego. Jeśli wyprowadzenie jest oznaczone jako wejście, będzie oczywiście miało tylko jedną komórkę skanowania.

Interfejs JTAG jest czteroprzewodowy: Test Data In (TDI), Test Data Out (TDO), Test Clock (TCK) i Test Mode Select (TMS). TCK jest asynchronicznym sygnałem zegarowym, używanym do taktowania danych, wprowadzanych przez TDI, a wyprowadzanych z TDO. Wyprowadzenie TMS służy do kontrolowania sterownika TAP zarządzającego pracą rejestru. Jeśli się chce przejąć kontrolę nad wyprowadzeniem i wprowadzić do układu dane, które pojawią się w jego wyprowadzeniach, wystarczy do sterownika TAP wprowadzić polecenie przejścia układu do trybu EXTEST.

Odtąd każdy bit wprowadzany do rejestru przesuwnego jest doprowadzany do odpowiedniego wyprowadzenia. Zalety takiego rozwiązania polegają na tym, że plik BDSL jest bezpłatny, obwody skanowania krawędziowego są wbudowane w układach JTAG, a szczegóły dostępu do maszyny stanu JTAG (zwanej sterownikiem TAP) są dobrze udokumentowane w IEEE 1149.1 i w licznych dokumentach. Jego wadą jest konieczność poświęcenia czasu i wysiłku na implementację.

Ale są dostępne programy narzędziowe, które mogą ten proces jeszcze uprościć. Do wyprowadzeń układu BGA można przyłączyć wirtualne LED i przełączniki, które pomagają w monitorowaniu i sterowaniu testowanych sygnałów, a rejestrator skryptów pozwala opracowującemu tworzyć proste procedury testowania wraz z pętlami i warunkami. Skrypt jest przechowywany w zgodnym ze standardem przemysłowym pliku SVF, który może być odtwarzany w JSCAB lub każdym odtwarzaczu SVF. Umożliwia to bardzo szybkie testowanie wielu płytek i błyskawiczne odnajdywanie niesprawnej.

Oprogramowanie do testów krawędziowych

Oprogramowanie do testowania poprawności montażu układów scalonych na PCB oraz ciągłości połączeń między nimi metodą ścieżki krawędziowej JTAG ma w swojej ofercie wielu producentów. Wspólną cechą narzędzi tego typu jest funkcja wprowadzenia wektorów testowych na wybrane wejścia układu oraz śledzenia zmian sygnałów na odpowiednich wyjściach.

W niektórych z nich implementowane są różne dodatkowe funkcje diagnostyczne, programy te różnią się też między sobą sposobem prezentacji wyników testów. Większość z tych narzędzi umożliwia również programowanie układów cyfrowych za pośrednictwem interfejsu JTAG.

JTAG ProVision

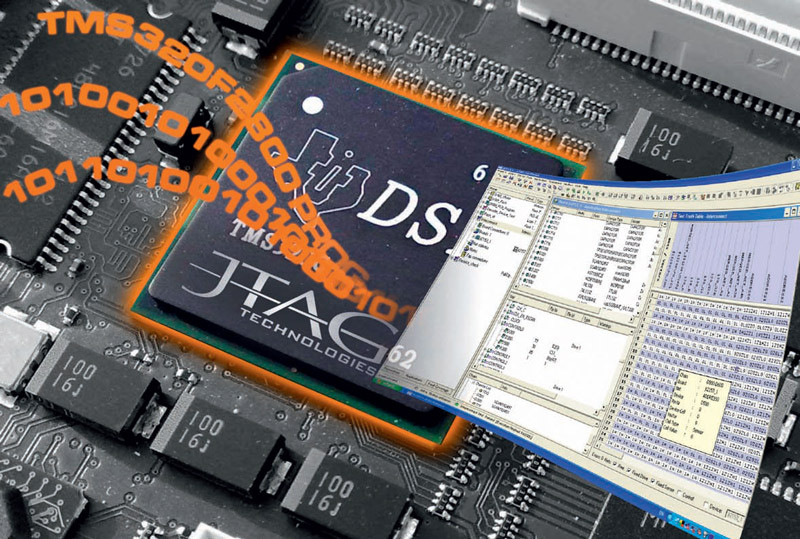

JTAG Technologies to jeden z pionierów i liderów rynku oprogramowania do testów krawędziowych. Dystrybucją oferowanego przez nią oprogramowania zajmuje się warszawski WG Electronics. Sztandarową aplikacją tego dostawcy jest JTAG ProVision - program do testów boundary scan i programowania ISP (In System Programming).

Umożliwia on automatyzację i intuicyjne projektowanie testów ścieżką krawędziową i ich realizację różnego typu (board-level, system-level, board-to-board), programowanie pamięci Flash (zaimplementowano w nim funkcje takie jak m.in.: sprawdzenie skasowania zawartości pamięci Flash (blankcheck), read-ID, kasowanie pamięci, programowanie oraz weryfikacja poprawności programu zapisanego do pamięci) oraz programowanie układów PLD (obsługiwane formaty plików: SVF, JEDEC, JAM, STAPL, IEEE 1532).

W programie JTAG ProVision większość zadań (w tym m.in. rozpoznawanie topologii łańcucha JTAG, rozpoznawanie urządzeń kompatybilnych ze standardami IEEE 1149.1 i IEEE 1149.6 oraz tych bez interfejsu JTAG, a także określanie wartości granicznych sygnałów testujących na podstawie modeli komponentów) została zautomatyzowana. Program JTAG ProVision jest ponadto zintegrowany z aplikacją JTAG Visualizer - systemem zarządzania danymi umożliwiającym ich graficzną prezentację.

JTAG Visualizer ułatwia analizę wyników skanowania układów po ścieżce krawędziowej dzięki temu, że są one nanoszone bezpośrednio na schemat układu lub płytki. Funkcje takie jak podświetlanie lub kolorowanie komponentów oraz ścieżek sygnałowych pozwalają szybciej zlokalizować wadliwe elementy urządzenia lub przerwane połączenia, w tym grupować różne typy uszkodzeń, przypisując im różne sposoby oznaczenia (np. różne kolory).

XJAnalyser i XJEase

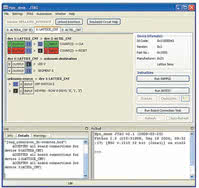

Przykładem narzędzi do testów typu boundary scan jest także oprogramowanie firmy XJTAG, którego dystrybucją w Polsce zajmuje się firma Quantum. Producent ten oferuje m.in. aplikacje XJAnalyser i XJEase. Pierwsza z nich służy do testowania oraz programowania urządzeń w łańcuchu JTAG, także układów BGA. W programie tym można wybrać jeden z trzech sposobów przedstawienia wyników diagnostyki: w postaci graficznej prezentacji łańcucha JTAG, w formie tekstowej listy pinów oraz podglądu stanu wybranych wyprowadzeń (rys. 2).

W ostatnim trybie istnieje możliwość grupowania pinów w magistrale oraz zapisywania ich wartości do kompletnej szyny. Oprócz tego XJAnalyser umożliwia importowanie plików SVF oraz STAMPL/ JAM i programowanie w systemie układów CPLD lub FPGA, także w łańcuchach JTAG złożonych z kilku urządzeń. XJEase służy z kolei do sprawdzania ciągłości połączeń między układami. Umożliwia wykrycie zwarć i przerw pomiędzy liniami sygnałowymi oraz zwarć do masy lub zasilania na podstawie informacji z plików BSDL oraz z pliku netlisty (obsługiwane typy plików netlisty to: EDIF 2, RINF, Protel i PADS PCB).

Wyniki prezentowane są w postaci listy numerów pinów, między którymi połączenie zostało przerwane. W XJEase można też uruchomić bardziej zaawansowane testy, na przykład wysyłanie i odbieranie ramek ethernetowych. Aplikację tę można również wykorzystać do programowania urządzeń z interfejsem JTAG (CPLD, FPGA) i komponentów bez tego interfejsu (na przykład pamięci Flash).

Hpe_JTAG

Poza wiodącymi na rynku produktami firm JTAG Technologies i XJTAG dostępny jest szereg mniej znanych produktów. Przykładem jest oprogramowanie diagnostyczne Hpe_JTAG, którego główne funkcje to sprawdzanie jakości połączeń lutowniczych układów BGA, diagnostyka poprawności wykonania ścieżek na płytce PCB oraz połączeń pomiędzy układami na płytce, testowanie układów elektronicznych na płytce (pamięci, rejestrów, wyświetlaczy) oraz debugowanie projektów CPLD/FPGA.

Specyfikację techniczną oprogramowania Hpe_JTAG zamieszczono w tabeli 1. Oprócz przedstawionych przykładów programów do testów ścieżką krawędziową dostępnych w ofercie polskich dystrybutorów na świecie narzędzia takie oferują też m.in. firmy Corelis (www.corelis.com) oraz Asset (www.assetintertech.com).

Monika Jaworowska

Krzysztof Pochwalski

Printor

www.printor.pl