Przykładem takiej normy, stosowanej przez renomowanych producentów PCB, w tym TS PCB, jest IPC-600H. Ten oraz inne standardy klasyfikują oraz określają dopuszczalny zakres defektów wykonania poszczególnych warstw obwodu, w tym mozaik. O ile występowanie drobnych uchybień w odwzorowaniu kształtów mozaiki jest dopuszczalne, o tyle pełna zgodność struktury i liczby odwzorowanych sieci elektrycznych z projektem musi zostać zachowana.

Celem wykonywanego u producenta PCB testowania obwodów drukowanych (bare board testing) jest sprawdzenie, czy spełniają one wytyczne klientów i normy branżowe, a w szczególności, czy sieci elektryczne w wyprodukowanych obwodach są w pełni zgodne z dokumentacją projektową. W artykule omówiona zostanie systematyka testowania oraz najpopularniejsze metody i techniki testowania mozaik płyt drukowanych wraz z ich cechami charakterystycznymi i ograniczeniami.

Z uwagi na obszerność tematyki artykuł podzielono na dwie części. Niniejsza, pierwsza część poświęcona zostanie klasyfikacji metod testowania obwodów oraz testowaniu elektrycznemu przy wykorzystaniu testerów z ruchomymi sondami. W drugiej części, która ukaże się w kolejnym numerze "Elektronika", przedstawione zostaną testery ostrzowe o nieruchomych sondach oraz testowanie optyczne.

Systematyka testowania

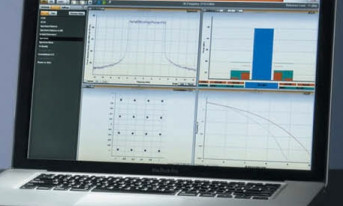

Klasyfikację metod testowania warstw przewodzących PCB przedstawiono na rysunku 1. Upowszechniły się dwa główne kierunki rozwojowe: testowanie elektryczne (electrical testing, e-test), podczas którego weryfikowana jest struktura sieci rzeczywistego obwodu względem jego projektu oraz testowanie optyczne (Automated Optical Inspection, AOI) bazujące na graficznym porównaniu obrazów mozaik obwodu z wzorcowymi obrazami wygenerowanymi z dokumentacji projektowej.

W testowaniu elektrycznym wyróżnia sie dwie techniki dostępu sond pomiarowych do punktów testowych mozaik obwodu poprzez: testery z ruchomymi sondami pomiarowymi (flying probe testers) oraz testery ostrzowe, w których nieruchome sondy występują w postaci igieł o średnicach i rozmieszczeniu dopasowanym do rozmiaru i położenia pól kontaktowych testowanego obwodu (fixed probe testers, bed of nail testers).

Testowanie elektryczne

Test elektryczny wykorzystuje fakt, że lista sieci elektrycznych obwodu, określana z jęz. angielskiego jako netlist, stanowi sygnaturę charakterystyczną dla każdego obwodu. Najczęściej spotykanymi defektami mozaik, które modyfikują netlistę, są uszkodzenia katastroficzne w postaci zwarć (shorts) pomiędzy różnymi sieciami oraz rozwarć (opens).

Test elektryczny wykorzystuje fakt, że lista sieci elektrycznych obwodu, określana z jęz. angielskiego jako netlist, stanowi sygnaturę charakterystyczną dla każdego obwodu. Najczęściej spotykanymi defektami mozaik, które modyfikują netlistę, są uszkodzenia katastroficzne w postaci zwarć (shorts) pomiędzy różnymi sieciami oraz rozwarć (opens).

Zwarcia takie redukują liczbę sieci, natomiast rozwarcia mogą generować nowe dodatkowe sieci. Znacznym ułatwieniem testowania elektrycznego jest duża dostępność węzłów sieci, ponieważ każdy z nich jest punktem testowym, do którego można podłączyć aparaturę pomiarową testera.

Weryfikowanie netlisty wykonywane jest drogą dwóch testów rezystancyjnych: ciągłości (continuity test) oraz izolacji (isolation test). Podczas obu testów badana jest rezystancja, przy czym dla testu ciągłości - pomiędzy punktami testowymi w obrębie jednej sieci, a dla testu izolacji - pomiędzy daną siecią i punktami innych sąsiednich sieci elektrycznych (adjacent nets).

Zasady testu rezystancyjnego, a w szczególności klasyfikacji wyników pomiarów rezystancji, definiuje norma IPC9252. Wg niej rezystancja pomiędzy punktami testowymi o wartościach do 10 Ω świadczy o ich zwarciu, co oznacza, że punkty przynależą do tej samej sieci. Pomiar jest interpretowany jako rozwarcie w przypadku uzyskania rezystancji rzędu 10 MΩ i więcej.

Obszar pomiarowy pomiędzy punktami 10 Ω oraz 10 MΩ oznacza występowanie upływności pomiędzy punktami testowymi i ze względu na niejednoznaczność interpretacji jest przez tester wykrywane jako błędny pomiar. Tego typu błędy mogą powstawać wskutek niedokładnego kontaktu sond pomiarowych z powierzchnią punktów testowych spowodowanego np. zabrudzeniem lub uszkodzeniem sond.

Defekty te wymagają dodatkowej weryfikacji poprzez ponowny test po oczyszczeniu powierzchni kontaktowych lub przy wykorzystaniu stacji napraw PCB (fault station), która ułatwia ponadto określenie miejsc izolacji lub zwarć sieci na podstawie logów testera.

Testery z ruchomymi sondami

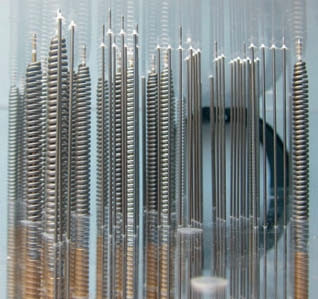

Rys. 2. Głowica testera palcowego uzbrojona w sondę (a) oraz najbardziej popularne typy stosowanych sond (b)

Zasada działania tego typu testerów, nazywanych także palcowymi, polega na dokonywaniu pomiarów za pomocą głowic pomiarowych wyposażonych w sondy poruszające się z obu stron nieruchomo zamocowanego obwodu drukowanego (rys. 2a). W najbardziej powszechnej konfiguracji tester dysponuje czterema kanałami pomiaru rezystancji, połączonymi z czterema niezależnymi sondami (rys. 2b), po dwie na każdą stronę płyty.

Zaletą niewielkiej liczby kanałów pomiarowych jest możliwość łatwego rozszerzenia ich funkcjonalności. Najpopularniejsze przystawki sprzętowe oferują m.in.: pomiar bardzo małych rezystancji za pomocą zacisków Kelvina, badania impedancji linii transmisyjnych oraz upływności izolacji przy pobudzeniu wysokimi napięciami rzędu setek woltów (HiPot testing).

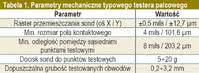

Najistotniejsze parametry mechaniczne testera palcowego uwarunkowane są przede wszystkim właściwościami serwomechanizmów odpowiadających za poruszanie sondami. Charakteryzują się one dużą szybkością i wysoką precyzją pozwalającą powtarzalnie pozycjonować sondy pomiarowe w osiach X i Y z krokiem na poziomie 0,5 mils, a nawet mniej, co pozwala na ich dokładne trafianie w niewielkie i gęsto położone pola kontaktowe np. układów scalonych SMD. Parametry układu mechanicznego warunkują dolną granicę rozmiaru pól kontaktowych, minimalną odległość pomiędzy sąsiednimi punktami testowymi oraz odpowiadają za siłę docisku sond do pól kontaktowych. Te oraz inne parametry typowego testera palcowego zestawiono w tabeli 1.

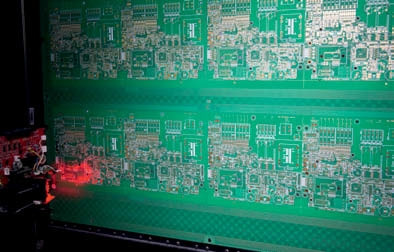

By zachować możliwie najwyższą powtarzalność trafiania sond w punkty testowe, konieczne jest dokładne zbazowanie (board registration) mechaniki względem punktów referencyjnych rozmieszczonych na krańcach testowanego formatu produkcyjnego. Proces ten ułatwiają kamery CCD, po jednej na każdą stronę obwodu, dające powiększony obraz fragmentów obwodu w otoczeniu rzeczywistych punktów referencyjnych.

Na obrazy te nakładane są obrysy kolejnych pól kontaktowych, które zdefiniowano w programie testu jako punkty referencyjne. Operację bazowania przedstawiono na rysunku 3, gdzie lewy rysunek to fragment obwodu z naniesionym położeniem punktu referencyjnego, a prawy jest rzeczywistym obrazem obwodu, na którym zgrano położenie punktu referencyjnego i odpowiadającego mu pola kontaktowego.

Prędkości i przyspieszenia serwo mechanizmów ma bezpośredni wpływ na szybkość testowania wyrażaną w liczbie punktów testowych na minutę oraz wynikający z niej czas testu. Dla przykładowego testera z rodziny Ultim8 firmy Mania szybkość testowania dochodzi do 5 tys. punktów na minutę. Nie bez znaczenia na szybkość testera ma także oprogramowanie testera, które optymalizuje sekwencje ruchów po szczególnych sond w taki sposób, aby zminimalizować konieczność częstego ich przemieszczania na większe odległości.

Pomimo zastosowania szybkiej mechaniki i usprawniania sekwencji przemieszczania głowic pomiarowych gwarantujących przetestowanie nawet kilku tysięcy punktów testowych na minutę, czas testu pojedynczego formatu produkcyjnego zawierającego skomplikowane i upakowane obwody HDI może dochodzić do kilkunastu minut lub nawet więcej.

Długi czas testu staje się zasadniczym ograniczeniem testerów palcowych, także w przypadku obwodów o niewielkich rozmiarach mogących wystąpić na pojedynczym formacie w liczbie kilkuset sztuk. Aby zredukować czas testowania, wielu producentów proponuje swoje własne autorskie optymalizacyjne rozwiązania sprzętowe i programowe. Przykładowe techniki optymalizacyjne zostaną omówione na bazie rozwiązań firmy Gardien - światowego dostawcy urządzeń i rozwiązań technologicznych w dziedzinie testowania obwodów drukowanych.

Wstępny test pojemnościowy

Rys. 4. Tester Acceler8 (a) oraz widok jednego z modułów jego głowicy pomiarowej uzbrojonego w sondy (b)

Jedną z metod redukcji czasu testowania jest zastosowanie wstępnego testu pojemnościowego, poprzedzającego test rezystancyjny. Polega on na obliczeniu pojemności sieci elektrycznych na podstawie projektu i porównywaniu ich we wszystkich rzeczywistych obwodach znajdujących się na formacie produkcyjnym.

O możliwości użycia testu pojemnościowego oraz doborze sieci decyduje oprogramowanie, które analizuje rozkład mozaik w badanym obwodzie. Podstawowym kryterium zastosowania testu pojemnościowego jest obecność w mozaikach obszarów referencyjnych o dużym wypełnieniu miedzią, względem których możliwe jest określenie pojemności sieci położonych na pozostałych warstwach.

Podstawową zaletą tego testu jest znaczne skrócenie procedury pomiarowej, ponieważ jedna lub dwie sondy stale dotykają punktów testowych warstwy sieci referencyjnej, a pozostałe sondy badają pojemność pozostałych sieci za pomocą pojedynczego dotknięcia sondy. W przypadku wykrycia znacznego odchylenia pojemności sieci w jednym z obwodów na formacie produkcyjnym następuje automatyczne przełączenie trybu testowania do testu rezystancyjnego, w celu dokładnej weryfikacji sieci tego obwodu.

Inną ciekawą koncepcję zastosowano w testerze Acceler8 firmy Gardien (rys. 4a), wykorzystywanym w TS PCB. Polega ona na wykonaniu zgrubnego testu wstępnego na specjalnym testerze, w którym głowica pomiarowa składa się z układu 4096 sond i jest wykonana w formie dywanu z delikatnych miedzianych włosków rozmieszczonych ze stałym rastrem (rys. 4b).

Przed rozpoczęciem testu konieczne jest pełne przetestowanie pojedynczego formatu produkcyjnego na testerze palcowym w celu zebrania wektora danych uczących dla Acceler8, na którego bazie oprogramowanie wyznacza, jakie sondy głowicy będzie można wykorzystać z uwzględnieniem rozkładu punktów testowych na formacie. Następnie kolejne formaty kierowane są już na tester Acceler8, gdzie podczas procedury pomiarowej omiatane są włoskami sond z jednej, a po przełożeniu, z drugiej strony.

Na podstawie zebranych danych wyznaczane są wyniki testu ciągłości i izolacji. Dla każdego formatu oprogramowanie analizuje wyniki pomiarów i określa, ile procent sieci zostało przetestowanych oraz generuje skrócony program testu uzupełniającego dla pozostałych sieci na tester palcowy. W zależności od układu mozaik uzyskuje się w ten sposób łączne skrócenie czasu testowania od 30 do ponad 50%. Ze względu na wydłużony proces nauki testera Acceler8 zysk czasu testu widoczny jest już od kilku formatów produkcyjnych.

Oferowany przez testery palcowe czas testu jest akceptowalny przede wszystkim w produkcji prototypowej i małoseryjnej. Takiemu wykorzystaniu sprzyja także niski koszt uruchomienia, ponieważ przygotowanie procedury testowej odbywa się wyłącznie w sferze programowej poprzez przygotowanie programu do testowania i nie wymaga dodatkowych inwestycji sprzętowych.

Podsumowanie

W pierwszej części artykułu omówiono potrzeby poprodukcyjnej weryfikacji obwodów drukowanych oraz przedstawiono systematykę metod testowania obwodów drukowanych. Scharakteryzowano technikę elektrycznego testowania mozaik PCB przy wykorzystaniu testerów z ruchomymi sondami pomiarowymi oraz zaprezentowano różne rozwiązania programowe i sprzętowe stosowane w celu zwiększenia wydajności testerów palcowych.

Druga część artykułu będzie poświęcona charakterystyce testowania elektrycznego za pomocą testerów ostrzowych, a ich parametry zostaną porównane z testerami palcowymi. Omówiona zostanie także technika optycznego testowania obwodów drukowanych oraz jej możliwości wykrywania defektów katastroficznych oraz jakościowych warstw przewodzących.

TS PCB Techno-Service S.A.

www.pcb-technoservice.eu