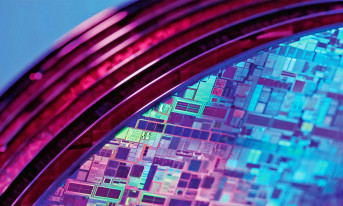

Chip Ponte Vecchio będzie wytwarzany w litografii 7 nm i ma być pierwszym procesorem graficznym Intela opartym o architekturę eX. Układ ten wykorzysta również firmowe rozwiązania, takie jak Intel Foveros 3D, EMIB, pamięć dużej przepustowości i standard Compute Express Link.

Intel twierdzi, że jego zorientowane na przetwarzanie danych rozwiązania technologiczne, w tym oneAPI (które również zostało zaprezentowane na Supercomputing 2019) - stanowią podstawę dla konwergencji eksaskalowych obciążeń HPC i AI w systemie Aurora, w Argonne National Laboratory.

Aurora jest pierwszym amerykańskim systemem eksaskalowym, który w pełni wykorzysta cały wachlarz technologii opracowanych przez Intela - bazując na platformie Intel Xeon Scalable i wykorzystując procesory graficzne oparte na architekturze Xe, a także rozwiązania w segmencie pamięci nieulotnej i łączności Intel Optane DC. Architektura węzła obliczeniowego Aurora będzie zawierać dwa procesory Intel Xeon Scalable o nazwie kodowej Sapphire Rapids, wykonane w procesie technologicznym 10 nm, i sześć układów graficznych Ponte Vecchio. System ten będzie obsługiwać 10 PB pamięci operacyjnej i ponad 230 PB na gromadzenie danych.

OneAPI zapewnia ujednolicony i uproszczony model programowania do tworzenia aplikacji w heterogenicznych architekturach, w tym procesorach CPU, GPU, układach FPGA i innych akceleratorach. Opracowane przez Intela rozwiązanie zapewnia twórcom oprogramowania zunifikowane i otwarte środowisko programistyczne na dowolnej architekturze bez utraty na wydajności i eliminacji złożoności oddzielnych baz kodu wielu języków programowania oraz różnych narzędzi.

Źródło: DigiTimes