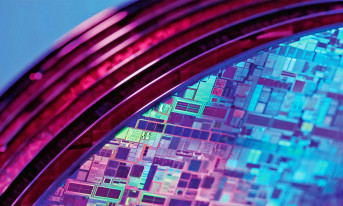

Obecnie w technologii 5 nm TSMC wytwarza chipy na masową skalę z zadowalającym wskaźnikiem wydajności. Firma oczekuje szybkiego wzrostu wykorzystania zasobów dla litografii 5 nm w drugiej połowie 2020 roku, w związku z silnym wzrostem zapotrzebowania na chipy do urządzeń mobilnych i aplikacji HPC.

Sprzedaż chipów w 5-nanometrowej litografii będzie odpowiadać za 10% całkowitych przychodów TSMC w bieżącym roku. CEO spółki dodał, że proces ten będzie wykorzystywany przez długi czas, podobnie jak 7, 16 i 28 nm.

W przypadku 7-nanometrowej litografii TSMC, na którą składają się technologie N7, N7+ i N6, dwie ostatnie wykorzystują proces produkcyjny EUV. Wygenerowana tegoroczna sprzedaż z tej technologii będzie odpowiadać za 30% całkowitych przychodów TSMC.

Wendell Huang, CFO w TSMC wskazuje, że tegoroczne nakłady inwestycyjne firmy zamykają się w przedziale 15-16 mld dolarów. Pomimo krótkiej niepewności spowodowanej pandemią wirusa oczekuję się, że aplikacje związane z 5G i HPC będą w ciągu najbliższych kilku lat nadal zwiększać popyt na zaawansowane procesy technologiczne.

Źródło: DigiTimes