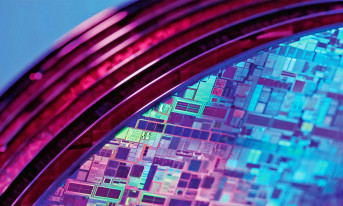

Zakład, który będzie realizował chipy w litografii 2 nm zlokalizowany jest w parku naukowo-technologicznym w Hsinchu na Tajwanie, a uruchomienie produkcji zaplanowano na 2024 rok.

- Pierwsza fabryka TSMC na Tajwanie wykorzystująca litografię 3 nm zostanie uruchomiona w roku 2021, a masowa produkcja ruszy w 2022 roku - powiedział Zhuang Zishou, dyrektor tajwańskiego zakładu foundry TSMC.

Według doniesień zakład R&D specjalizujący się w procesie 3 nm w Hsinchu na Tajwanie pomyślnie przeszedł weryfikację EIA i oczekuje się, że nadrobi zaległości w realizacji planów masowej produkcji. TSMC ujawniło również, że zakład wytwarzający 2 nm chipy ma powstać 5 lat później w Hsinchu. Jednym z powodów wyboru lokalizacji jest uniknięcie zjawiska drenażu mózgów, czyli skłaniania specjalistów wysokiej klasy do podejmowania pracy w krajach uprzemysłowionych przez zapewnienie im lepszych warunków ekonomicznych i nowoczesnej organizacji pracy. Obecnie TSMC posiada w Hsinchu około 7 tys. specjalistów w dziedzinie badań i rozwoju procesów półprzewodnikowych.

Według przygotowanych danych przez TSMC, proces 2 nm ma ogromne znaczenie. Przez dziesięciolecia postęp w przemyśle półprzewodnikowym był zgodny z prawem Moore'a. Określa ono, że co 18 do 24 miesięcy podwaja się liczba komponentów, które mogą być umieszczone na płytce krzemowej, a wydajność całego układu scalonego rośnie dwukrotnie.

Zgodnie z oficjalną informacją fabryka półprzewodników TSMC stanie się pierwszym zakładem, który ogłosił rozpoczęcie badań i rozwoju w obszarze litografii 2 nm. W chwili obecnej nie zostały ujawnione konkretne szczegóły dotyczące specyfikacji tego procesu.

Źródło: volanews