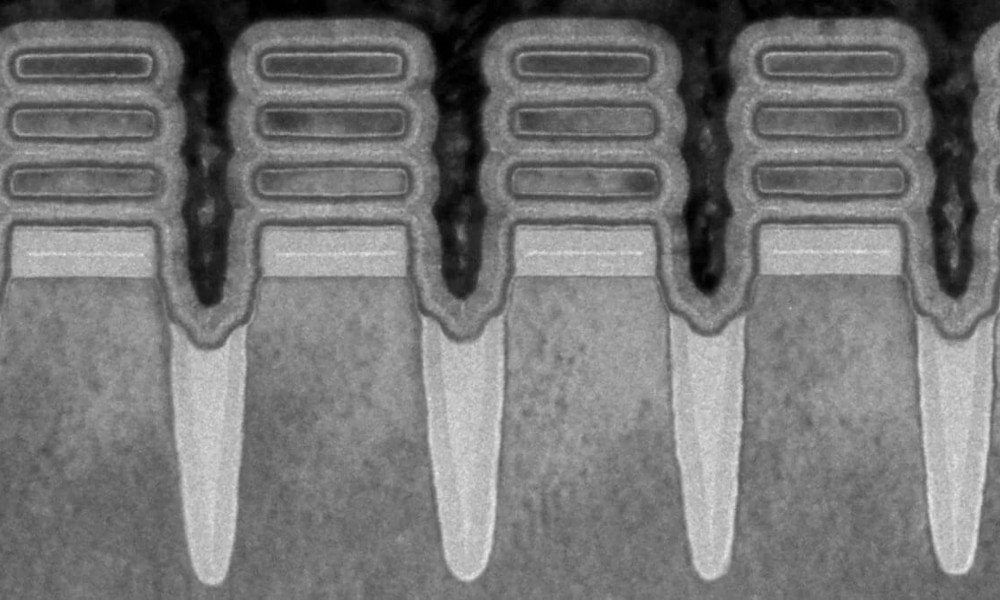

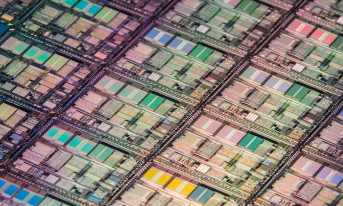

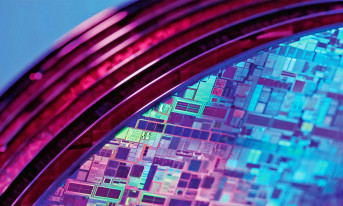

W projektach chipów już są wykorzystywane struktury tranzystorów FET typu Gate-All-Around (GAA) o wielkości 3 nm. Architektura MBCFET (Multi-Bridge Channel FET) ma zredukować powierzchnię struktury o 35%, zapewnić wyższą o 30% wydajność lub niższe o połowę zużycie energii w porównaniu z 5-nanometrowym procesem.

Jednak Samsung Foundry nadal będzie udoskonalać swoją obecną technologię procesową FinFET, aby wspierać produkty specjalistyczne. Działanie te pozwolą utrzymać konkurencyjną pozycję dla aplikacji. Technologia FinFET 17 nm pozwala zredukować powierzchnię chipa o 43% i zapewnić wyższą wydajność o 39% lub 49% wzrost wydajności energetycznej w porównaniu z procesem 28 nm.

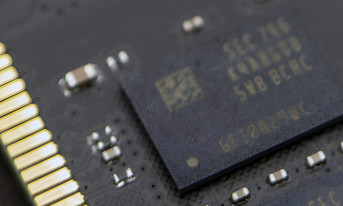

Samsung Foundry pracuje również nad 14-nanometrowym procesem dla pamięci MRAM pracującej z napięciem 3,3 V. Pamięć w tej postaci oferuje zwiększoną gęstość struktury i wyższą prędkość zapisu dla mikrokontrolerów MCU stosowanych w IoT i urządzeniach do noszenia. Oczekuje się, że w przypadku chipów radiowych RF przejście z 14- na 8-nanometrową litografię będzie coraz częstszym ruchem producentów w aplikacjach mmWave pracujących z częstotliwościami poniżej 6 GHz.

Poszukiwana jest również możliwości szerszego wykorzystania technologii 3D i architektury chipletów do heterogenicznej integracji układów radiowych i cyfrowych w jednej obudowie.

Źródło: EE News Europe