Według dr. Douglasa Yu, wiceprezesa TSMC odpowiedzialnego za integrację systemów, pomimo znacznych postępów dokonanych przez firmę w zaawansowanych opakowaniach wciąż napotykane są poważne przeszkody.

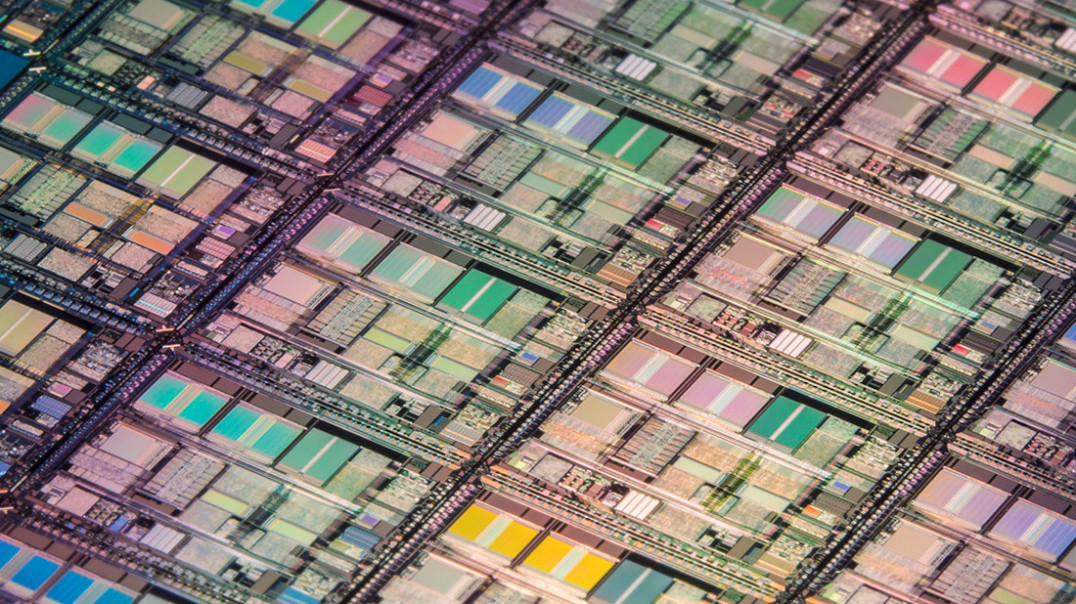

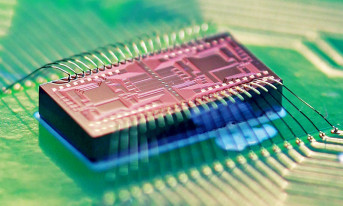

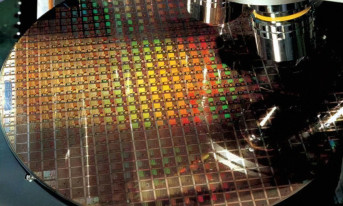

Uczestnicząc w wydarzeniu zorganizowanym przez SEMI, dr Yu zidentyfikował dwa wyzwania stojące przed TSMC, wynikające głównie z nieuniknionego przejścia od technologii front-end do back-end, które nastąpiło wraz z pojawieniem się zaawansowanych opakowań. Mimo że TSMC pracuje nad bardziej zaawansowanymi procesami niż 3nm, jeśli chodzi o pakowanie chipów, nadal tkwi na poziomie 2μm. W związku z tym kontrola kosztów i wydajność stają się przeszkodą, gdy TSMC wykorzystuje miedziane połączenia, aby zapewnić integrację heterogeniczną struktur chipów.

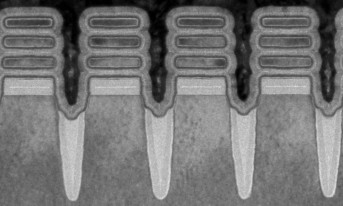

Z drugiej strony, precyzja stanowiłaby wyzwanie, gdyby TSMC zdecydował się na wykorzystanie tradycyjnego sprzętu w celu osiągnięcia heterogenicznej integracji. Ponieważ struktury IC stale są miniaturyzowane do skali nanometrowej, dodatkowe etapy procesu termicznego będą wymagane do układania chipów razem, co spowoduje zmianę struktury wafla, która ostatecznie wpłynie na precyzję połączeń elektrycznych.

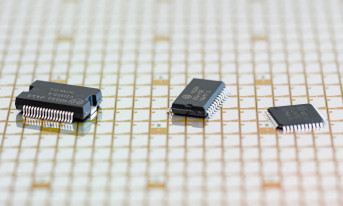

Według wiceprezesa TSMC, obecne plany TSMC koncentrują się na skalowaniu systemu, w tym na poprawie gęstości połączeń die-to-die, zmniejszając skok łączenia o 70% z każdą generacją. Kolejnym celem będzie ciągłe zwiększanie rozmiaru pakietów.

Źródło: Tech Taiwan