Wysiłki Intela nakierowane są przede wszystkim na techniki procesorów zbudowanych z bloków zwanych chipletami. Te, jako nowe stare rozwiązanie, już jakiś czas temu zelektryzowały branżę. Zainteresowanie nimi nasiliło się wówczas, kiedy po kilkudziesięciu latach obowiązywania prawa Moore'a, podczas których ewolucja technologiczna od komputerów PC, przez smartfony, po chmurę, możliwa była dzięki temu, że gęstość upakowania tranzystorów w jednostce powierzchni struktury półprzewodnikowej rosła zgodnie z przewidywanym przez nie harmonogramem, jego dalsze bycie w mocy stanęło pod znakiem zapytania. Wynikało to stąd, że charakterystyczny wymiar procesów w technologii krzemowej zaczął się zbliżać do wartości, przy których elementy struktur półprzewodnikowych stały się mniejsze niż najmniejsze znane wirusy i schodzenie poniżej nich zaczęło zajmować więcej czasu niż wcześniej i było również znacząco droższe.

Widząc zatem spowolnienie w nadążaniu za tempem narzucanym prawem Moore'a, o czym zaczęto mówić głośniej około 2016 r., w trosce o przyszłość branży elektronicznej oraz nie chcąc zawieźć odbiorców, przyzwyczajonych do tego, że w określonych odstępach czasu mogą oczekiwać innowacji w sprzęcie elektronicznym, zaczęto szukać alternatyw dla zmniejszania wymiaru charakterystycznego. Dlatego zdecydowano się, by odświeżyć oraz dostosować do nowych potrzeb koncepcję chipletów.

Czym jest chiplet?

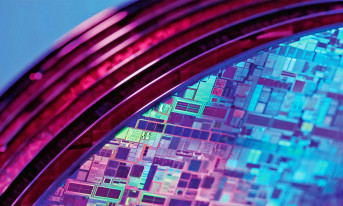

Jest to moduł w postaci struktury scalonej o określonej funkcjonalności. Wiele takich chipletów można łączyć w obrębie wspólnego podłoża w jeden układ scalony. Nasuwa się tu oczywista analogia z półprzewodnikowymi klockami Lego, z których można złożyć przykładowo procesor. Komunikacja między chipletami zapewniona jest przez sieć połączeń oraz kontaktów zrealizowanych w podłożu, w wersji podstawowej trochę na podobieństwo „zwykłych” PCB.

Kluczowym aspektem technologii tego typu modułów jest to, że są one dostępne jako zestandaryzowane bloki, które można dowolnie ze sobą kompletować. Zapewnia to dużą elastyczność w zakresie funkcjonalności i jej modyfikacji – jest ona tańsza i prostsza niż na przykład w układach SoC, w których bloki funkcyjne, wykonywane w obrębie jednej struktury scalonej, trzeba przy każdej zmianie funkcjonalności przeprojektować oraz ze sobą zintegrować. Tymczasem w przypadku chipletów, po wybraniu tych niezbędnych z puli już gotowych rozwiązań, wystarczy rozplanować połączenia między nimi.

Chiplety w procesorach AMD i Intela

Opinie o tym, że cała branża będzie się stopniowo przestawiać na technologię chipletów, pojawiały się już kilka lat temu. Eksperci zgodnie od tej pory twierdzą, że jest to ewolucja prawa Moore'a, a nie jego koniec. Na chipletach szybko swoje projekty zaczęły więc opierać największe firmy z branży – przykładowo AMD z tego typu „klocków” zbudowało procesory serwerowe Epyc, szacując, że dzięki temu koszt ich produkcji udało się obniżyć dwukrotnie w stosunku do tego, ile wyniósłby on, gdyby wykonano je w technologii tradycyjnej.

Wkrótce też okazało się, że rozwiązanie to nie jest zarezerwowane dla specjalistycznych rozwiązań, do których można zaliczyć procesory serwerowe, których jednym z bloków był moduł graficzny AMD. Zaprojektowano je z myślą o laptopach i wbudowano w te urządzenia marki Dell oraz HP. Szybko okazało się, że nowe podejście, mimo że obiecujące, wiąże się też z szeregiem wyzwań.

Jednym z nich jest zorganizowanie połączeń pomiędzy poszczególnymi chipletami (die-to-die) w płaszczyźnie (2D), bez strat mocy, opóźnień i ograniczeń przepustowości. Rozwiązania, które są stosowane w tym zakresie, określa się mianem technologii pakowania 2,5D.

Jak połączyć chiplety?

Najłatwiejszym sposobem skomunikowania chipletów na tym samym podłożu jest poprowadzenie w nim ścieżek sygnałowych. Jak pisaliśmy wyżej, podłożem jest zwykle struktura na wzór płytki drukowanej wykonana z warstw izolacyjnego materiału przeplatanych warstwami metalu, w których wytrawiono ścieżki. W zależności od jakości podłoża oraz standardu komunikacji, transmisja danych za pośrednictwem takiego medium wiąże się z dużymi stratami mocy i ograniczeniami przepustowości. Nie da się jednak ukryć, że jest to najtańsza opcja.

Alternatywą jest konstrukcja, w której wykorzystuje się krzemową przekładkę o powierzchni większej niż ta, którą razem zajmują wszystkie łączone za jej pośrednictwem chiplety. Ścieżki sygnałowe są wykonywane w krzemie i z wykorzystaniem przelotek TSV (Th rough Silicon Vias). W tej konstrukcji straty mocy są mniejsze, a przepustowość większa. Lecz jest to zarazem droższe rozwiązanie. Ta technika nakłada również ograniczenia na rozmiary chipletów.

Czym jest technologia EMIB?

Tytułowa technologia zaproponowana już kilka lat temu przez firmę Intel stanowi z kolei niejako połączenie obu wcześniej opisanych rozwiązań. Oznacza to, że w strukturach wykonanych w technice EMIB (Embedded Multi-die Interconnect Bridge) wewnętrzne połączenia o dużym zagęszczeniu w heterogenicznych układach scalonych wykonuje się, wbudowując w podłoże mostek. Jest to mały kawałek krzemu, osadzony jedynie przy krawędziach łączonych ze sobą modułów. Można też wprowadzić więcej niż jeden mostek między dwoma chipletami, jeżeli przykładowo wymagana jest większa przepustowość.

Generalnie koszt mostka jest niższy niż przekładki i przelotek TSV. Z drugiej strony osadzenie mostka w podłożu nie jest łatwe. Dlatego firma Intel poświęciła kilka lat i mnóstwo zasobów na udoskonalenie technologii EMIB pod kątem ograniczenia poboru mocy. Mimo trudności podejście to zastosowano w łączeniu chipletów dotychczas już w kilku produktach tego producenta, na przykład w układach FPGA rodzin Stratix i Agilex oraz procesorach serii Kaby Lake-G, w połączeniu GPU Radeon z pamięcią. Intel planuje również korzystać z tej przyszłościowej technologii w kolejnych generacjach procesorów, m.in. w tych z serii Meteor Lake.

Firma zapowiada też oczywiście dalszy rozwój tej technologii – w planach jest m.in. zmniejszenie rastra wyprowadzeń połączeń mostek–chiplet. Im jest to mniejsza wartość, tym więcej połączeń można zrealizować przy danym rozmiarze mostka. Pozwala to albo zwiększyć przepustowość transmisji, albo zmniejszyć rozmiar mostka. W pierwszej generacji układów w technologii EMIB parametr ten wynosił 55 μm, ale planowane jest jego zmniejszenie najpierw do 45 μm, zaś docelowo do 40 μm.

Foveros i nowe technologie na horyzoncie

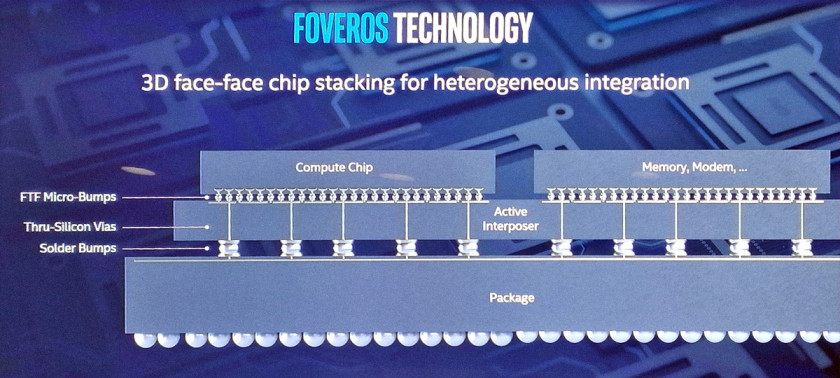

O ile technologia EMIB dotyczy łączenia chipletów w poziomie, o tyle tytułowe rozwiązanie integruje je w pionie – Foveros to nowa technologia Intela w zakresie pakowania 3D wielu chipletów w jednej obudowie. Są one umieszczane jeden na drugim i łączone ze sobą za pomocą mikrowyprowadzeń (o rozstawie 36 μm w procesorze Meteor Lake, który ma trafić na rynek w 2023). Przykładowa konstrukcja może się składać z podstawowej matrycy logicznej, na której znajdują się pozostałe komponenty, takie jak inna matryca logiczna, pamięć, FPGA, a nawet układy analogowe/radiowe.

Foveros nie został zaprojektowany w celu zastąpienia EMIB, jest raczej jej uzupełnieniem, te dwie technologie rozwiązują bowiem nieco inne problemy. Co więcej, można je nawet połączyć, tworząc jeszcze bardziej złożone produkty – takie podejście, polegające na umieszczeniu w jednej obudowie układów wykonanych w technologiach EMIB oraz Foveros, zaproponowane zostało w technologii Co-EMIB. Intel w planach ma również rozwój samej technologii Foveros. W tym zakresie pojawiła się ostatnio zapowiedź dwóch nowych rozwiązań: Foveros Omni oraz Foveros Direct. Nowością w Foveros Omni mają być konstrukcje miedzianych kolumn, którymi prowadzone będzie zasilanie i inne sygnały, z pominięciem przelotek TSV. Foveros Direct wyróżniać mają z kolei bezpośrednie połączenia miedź-miedź.

Monika Jaworowska