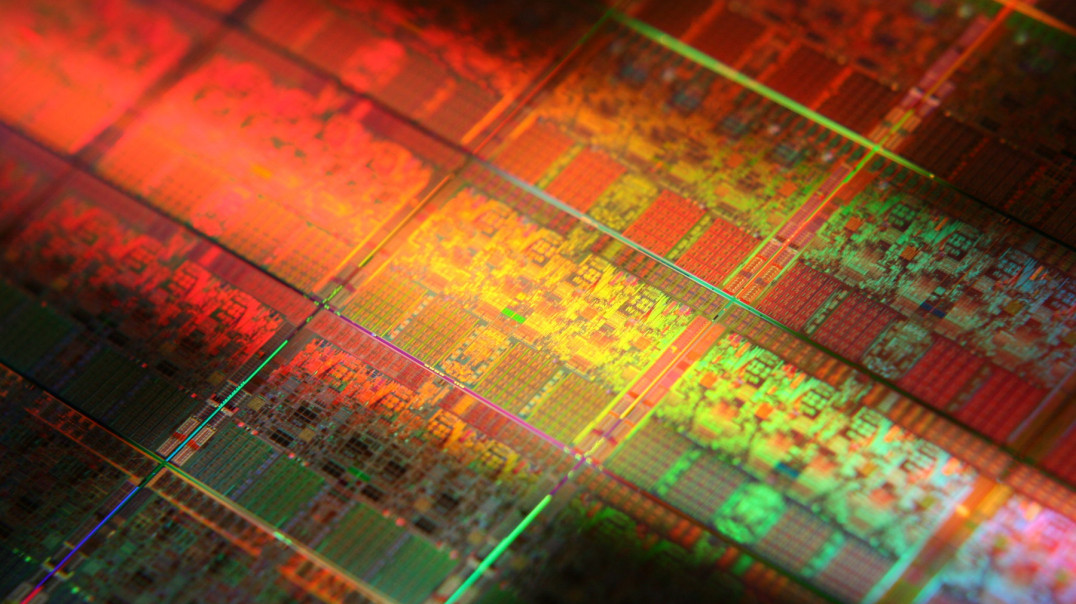

Firmy wskazują, że system chipletów typu roof-of-concept z powodzeniem demonstruje kluczowe technologie konstruowania układów HPC system-on-chip (SoC) z rdzeniami arm wykonanymi w procesie FinFET 7 nm, taktowanymi zegarem o częstotliwości 4 GHz. To rozwiązanie demonstruje również projektantom układów SoC dwukierunkową magistralę w formie siatki działającą z tą samą częstotliwością oraz metodologię projektowania chipletów połączonych niskonapięciowym interkonektem o transferze sięgającym 8 Gb/s na pin.

W porównaniu z tradycyjnym podejściem do układów SoC, które polegało na łączeniu każdego elementu w jedną matrycę, konstrukcja chipletów jest zoptymalizowana pod kątem nowoczesnych procesów HPC, które dzielą większe układy wielordzeniowe na mniejsze chipsety. To rozwiązanie umożliwia podział funkcji na mniejsze oddzielne matryce, które zapewnią elastyczność przy wytwarzaniu każdego chipletu w różnych procesach technologicznych. W celu zapewnienia wysokiej wydajności chiplety muszą komunikować się ze sobą za pośrednictwem gęsto upakowanych połączeń o dużej przepustowości.

Opracowany system chipletów składa się z podwójnego układu CoWoS w litografii 7 nm, a każda jednostka zawiera cztery procesory Arm Cortex-A72 i magistralę siatkową. Połączenia między chipletami typu die-to-die charakteryzują się skalowalną wydajnością energetyczną o wartości 0,56 pJ/bit, gęstością pasma wynoszącą 1,6 TB/s na mm² i niskonapięciowym interfejsem LIPINCON pracującym na poziomie 0,3 V.

Źródło: DigiTimes