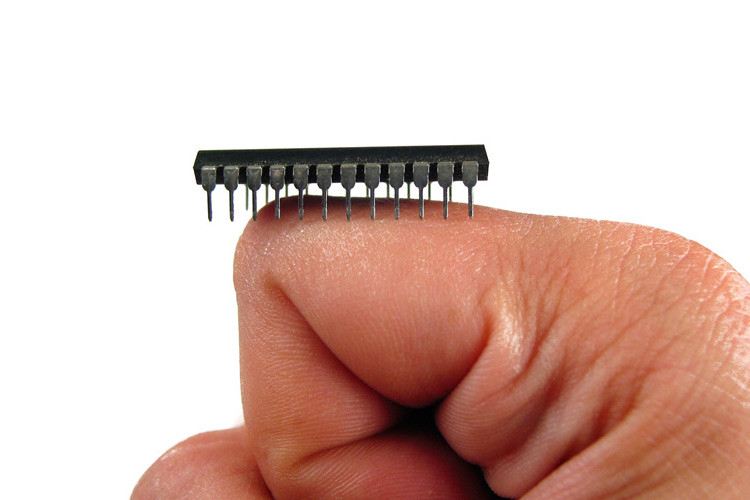

Pierwsze przełomowe, komercyjnie dostępne, układy scalone były pakowane w obudowach DIP (Dual In-line Packaging). Zastąpiły one ceramiczne i metalowe, hermetycznie zamykane obudowy, wykorzystywane do osłony układów scalonych dla wojska i lotnictwa. Te bowiem nie nadawały się do produkcji i użytku na masową skalę w sprzęcie komputerowym i elektronice użytkowej, które to zastosowania półprzewodników zaczynały się właśnie w szybkim tempie w tamtym czasie, czyli w latach 70. zeszłego wieku, rozwijać.

Początki obudowywania układów scalonych

Co ciekawe, początki technologii obudów DIP są do dziś owiane tajemnicą. Jest to niespotykane w branży elektronicznej, w której zazwyczaj wszelkie innowacje są ogłaszane z pompą i natychmiast zgłaszane do opatentowania.

W przypadku obudów DIP tymczasem nie jest nawet do końca pewne, kim są ich wynalazcy. Większość źródeł podaje, że za takich powinno się uznać pracowników firmy Fairchild Semiconductor: Dona Forbesa, Rexa Rice'a i Bryanta „Bucka” Rogersa. Przyjmuje się, że zaprojektowali oni obudowy DIP w 1964 roku. Do prac nad nowym typem opakowań skłoniło ich to, że liczba potrzebnych wyjść układów scalonych zaczynała przerastać maksymalną wykonalną liczbę wyprowadzeń w dotychczas dostępnych opakowaniach (najwyżej 10). Wiadomo także, że w swoim projekcie inżynierowie Fairchilda opierali się na konstrukcji opracowanej na potrzeby armii amerykańskiej przez inżyniera Yunga Tao z firmy Texas Instruments w 1962 roku, którą zoptymalizowano pod kątem cech istotnych w zastosowaniach wojskowych: odporności na wibracje, hermetyczności i rozpraszania ciepła.

Zadaniem Forbesa, Rice'a i Rogersa było wprowadzenie ulepszeń w projekcie TI uwzględniających wymogi elektroniki użytkowej i możliwości producentów układów scalonych. Kryterium projektowym była także łatwość rozplanowania rozmieszczenia komponentów na płytkach drukowanych i możliwości ich montażu – już wówczas bowiem zdawano sobie sprawę, że wraz ze wzrostem złożoności urządzeń elektronicznych liczba podzespołów PCB będzie rosła, co utrudni prowadzenie ścieżek.

Obudowy DIP

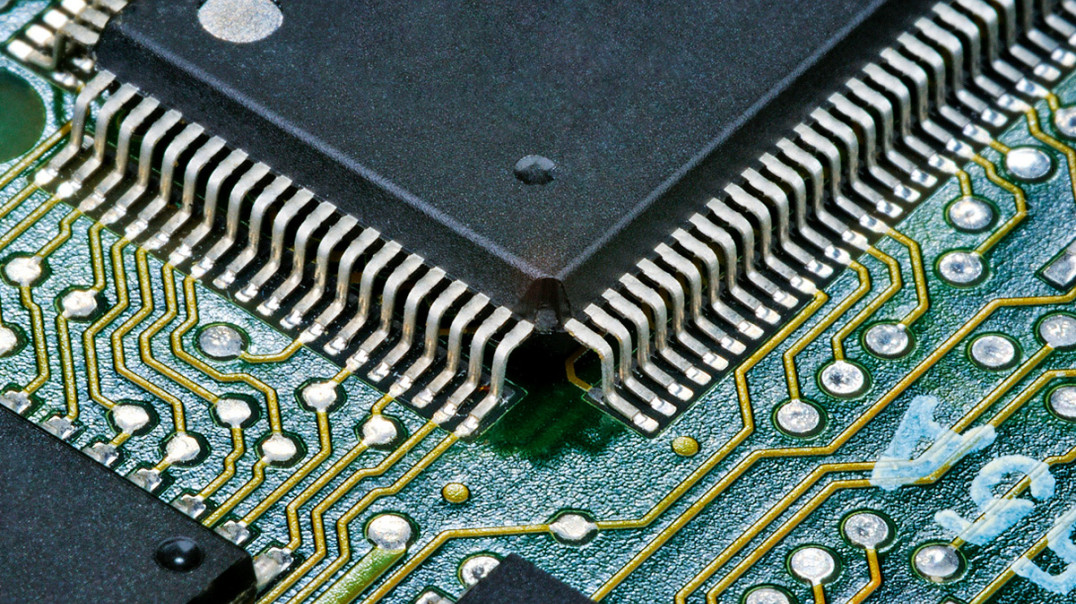

Wpłynęło to na rozmiary obudów DIP i rozstaw wyprowadzeń, a wymóg taniej i szybkiej masowej produkcji zdecydował o tym, że wykorzystano w nich metalową ramkę (leadframe), łatwo formowalną w procesie wytłaczania, do której mocowana była struktura półprzewodnikowa. W efekcie wszystkie etapy pakowania (wytłaczanie ramki, mocowanie układu scalonego, łączenie wyprowadzeń ramki z wyjściami struktury półprzewodnikowej) można było zrealizować w jednym ciągu technologicznym, zakończonym zagięciem pinów obudowy prostopadle do jej korpusu.

Wykonywane w ten sposób opakowania DIP trafiły do masowej produkcji w 1965 roku. Na początku były to obudowy ceramiczne, gdyż priorytetem było zachowanie hermetyczności w stopniu wymaganym w zastosowaniach wojskowych. Z czasem jednak ceramikę zaczęto zastępować tworzywami sztucznymi ze względu na mniej uciążliwe warunki pracy elektroniki użytkowej, dla których te materiały gwarantowały wystarczającą szczelność. Znacząco obniżyło to koszt jednostkowy produkcji. Dalsza ewolucja obudów DIP obejmowała głównie zwiększanie liczby wyprowadzeń i sposobu ich rozmieszczenia (SIP (Single In-line Package), ZIP (Zigzag In-line Package)). Kres ich możliwości osiągnięto dopiero około 2000 roku, nie ma jednak wątpliwości, że utorowały one drogę innym technologiom pakowania.

Technologia SMT

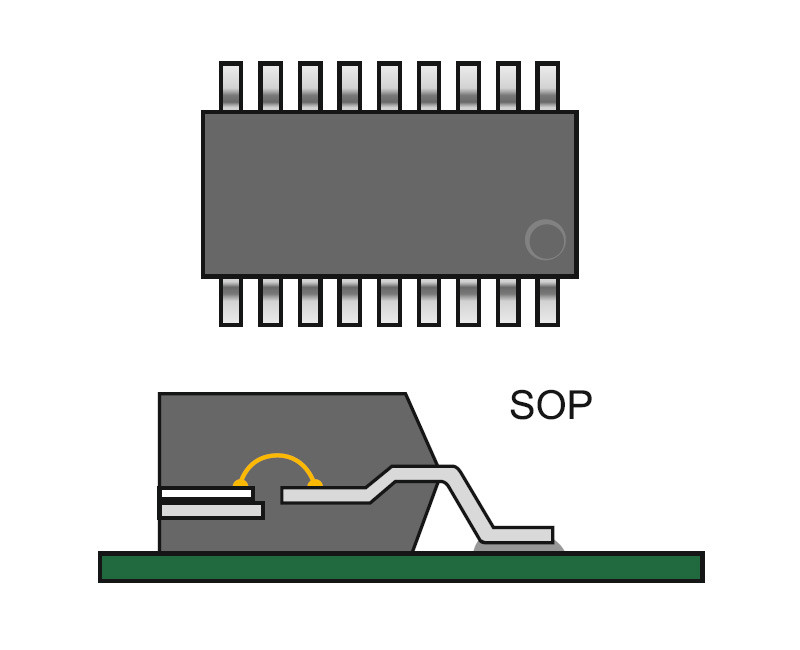

Krokiem milowym w historii technologii pakowania układów scalonych było przejście z obudów do montażu przewlekanego (Through Hole Technology, THT), jak DIP, na te montowane powierzchniowo (Surface Mounted Technology, SMT). Technika montażu powierzchniowego zyskała akceptację dopiero pod koniec lat 80. zeszłego wieku, choć została opracowana już w latach 60. Wynikało to stąd, że na przełomie lat 70. i 80., wraz z rosnącym popytem przede wszystkim na sprzęt komputerowy, w lutowaniu płytek drukowanych z konieczności zaczęły się upowszechniać rozwiązania zautomatyzowane.

Niestety elementy elektroniczne w obudowach do montażu powierzchniowego utrudniały automatyzację – często trzeba było zatrzymywać maszyny i operator musiał interweniować z powodu ich niedokładnego ułożenia na PCB. Problemem były też różnice tolerancji wymiarów i rozstawu otworów i wyprowadzeń. Spowolniało to lutowanie i w konsekwencji zwiększało koszty montażu. Dlatego kiedy zaproponowano alternatywę, w której wyprowadzenia podzespołów nie przechodzą przez płytkę, tylko przylutowuje się je bezpośrednio do powierzchni PCB, nastąpił przełom.

Co wyróżnia obudowy QFP?

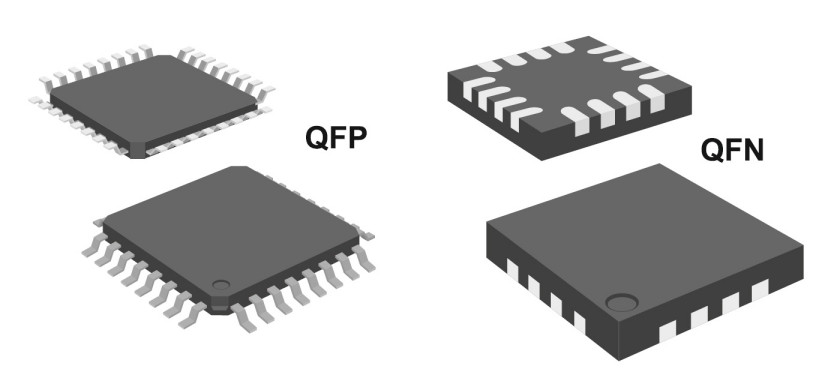

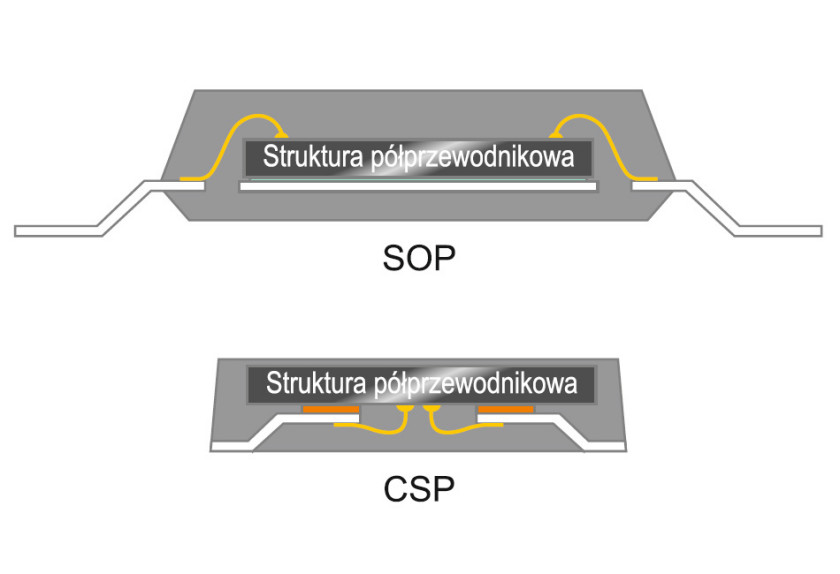

Przykłady obudów do montażu powierzchniowego to SOP (Small Outline Package) i wersje: CSOP (Ceramic SOP), DSOP (Dual SOP), SSOP (Shrink SOP), TSOP (Th in SOP), TSSOP (Thin Shrink SOP), MSOP (Mini/Micro SOP), QSOP (Quarter SOP). W 1986 przedstawiono, opracowane w Japonii, obudowy QFP (Quad Flat Package). Wyróżnia je duża gęstość wyprowadzeń, które są rozmieszczone ze wszystkich stron korpusu. Do tej grupy zalicza się m.in. BQFP (Bumpered QFP). Ich kanty są zakończone specjalnymi wypustkami chroniącymi piny, które łatwo jest wygiąć – ze względu na duże zagęszczenie wyprowadzeń takie ich uszkodzenie jest trudne, i przeważnie nieopłacalne, do naprawy. Przykłady obudów typu QFP to też: HQFP (Heat sinked QFP), zoptymalizowane pod kątem rozpraszania ciepła, ceramiczne CQFP (Ceramic QFP) oraz niskoprofilowe LQFP (Low profile QFP). Obudowy QFN (Quad Flat Non-leaded) mają z kolei płaskie wyprowadzenia rozmieszczone pod korpusem.

Obudowy BGA

QFP dominowały w latach 90. zeszłego wieku, równocześnie jednak opracowano kolejną generację obudów do montażu powierzchniowego w formacie BGA (Ball Grid Array) z wyprowadzeniami w postaci kulek wykonanych ze stopu lutowniczego w okach siatki na spodzie komponentu, na całej jego powierzchni albo na jej części. Mają one wiele zalet.

Najważniejsze to: mniejsze rozmiary w porównaniu do konkurencyjnych konstrukcji o podobnej liczbie wyprowadzeń, brak pinów, które mogłyby się wygiąć lub obłamać, samowyrównanie kulek lutowniczych na polach kontaktowych dzięki zjawisku napięcia powierzchniowego oraz lepsze właściwości elektryczne dzięki krótszym połączeniom (mniejsze rezystancja i indukcyjność) i mniejszy rozrzut wysokości przylutowanych wyprowadzeń względem płaszczyzny płytki drukowanej. Przeniesienie wyprowadzeń z boków na spód obudowy uznaje się za kolejny przełomowy krok w historii technologii pakowania układów scalonych.

Najpopularniejsze wersje obudów BGA to: PBGA (Plastic BGA), CBGA (Ceramic BGA) i TBGA (Tape BGA). Pierwsze, z tworzywa sztucznego, opracowane przez Motorolę, są najpopularniejsze. CBGA są wykonane na podłożu ceramicznym i mają metalową lub ceramiczną obudowę, z kolei TBGA mają elastyczne podłoże z poliimidu. Generalnie, obudowy PBGA charakteryzują średnie właściwości elektryczne i termiczne, są tanie i dość odporne na wpływ otoczenia. Najlepsze pod względem właściwości elektrycznych i cieplnych są obudowy ceramiczne, które wyróżniają się szczelnością i dużą odpornością na warunki w otoczeniu. Są jednak najdroższe. TBGA cechują natomiast dobre właściwości elektryczne, termiczne i średni koszt.

Technologia CSP

Kolejny skrót do rozszyfrowania, ważny w historii technologii pakowania układów scalonych, to CSP (Chip Scale Package). Opisuje on, wprowadzone we wczesnych latach 90. zeszłego wieku, podejście do pakowania, w którym rozmiar obudowy jest nie większy niż 1,2 razy od rozmiaru struktury półprzewodnikowej. Z tego wynika alternatywne rozwinięcie akronimu CSP – Chip Size Package. Warto zaznaczyć, że definicja obudowy CSP nie precyzuje, w jakiej dokładnie technologii ją wykonano, o ile tylko spełnia ona opisany wyżej warunek dotyczący stosunku rozmiarów opakowania i jego zawartości.

W celu sklasyfikowania obudów CSP wprowadzono ich podział na cztery kategorie: flex lub tape, w której podłożem jest materiał elastyczny, rigid, z podłożem z laminatu lub ceramicznym, leadframe i wafer-level, w której struktury scalone są umieszczane w obudowach jeszcze przed ich wyodrębnieniem z płytki półprzewodnikowej. W obudowach zaliczanych do kategorii CSP w zakresie sposobu łączenia pól kontaktowych struktury półprzewodnikowej z wyprowadzeniami obudowy stosuje się technikę montażu drutowego wirebonding jak i flipchip. W drugiej strukturę półprzewodnikową montuje się wierzchem z polami kontaktowymi do podłoża. Generalnie więc technologia CSP, zalety, które niesie ze sobą ograniczenie dotyczące rozmiarów obudowy, jak: mniejszy rozmiar, waga, poprawa właściwości elektrycznych oraz termicznych i niższy całkowity koszt produkcji, łączy z wyróżnikami innych technologii pakowania.

Czym jest WLP?

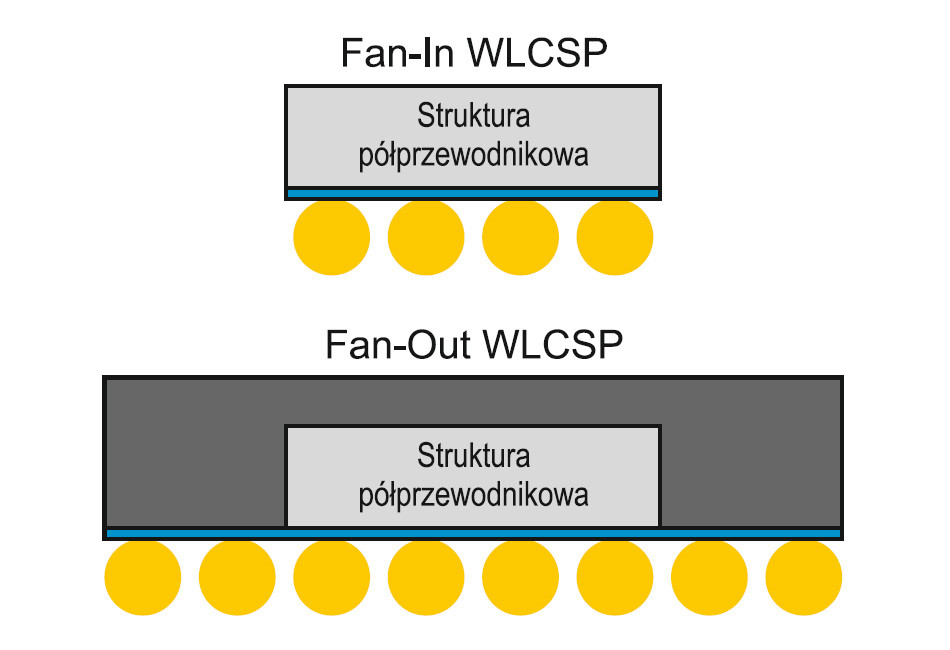

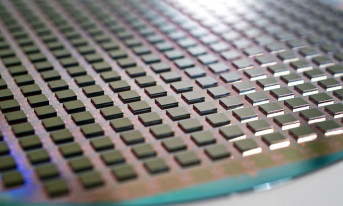

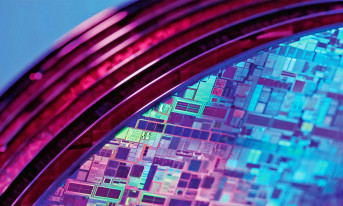

Ważnym typem obudów CSP są te w wersji WLP (Wafer-Level Packaging). Technika ta stanowi alternatywę dla pakowania każdego układu scalonego niezależnie po oddzieleniu go od innych wykonanych w tym samym cyklu produkcyjnym. Ma ona wiele zalet.

Przede wszystkim optymalizuje koszty i usprawnia proces produkcyjny oraz testowanie. Poza tym pozwala na produkcję mniejszych i cieńszych układów scalonych. Wyróżnia się dwa warianty techniki WLP: Fan-in oraz Fan-out.

Obudowy Fan-In WLP (FIWLP) i Fan-Out WLP (FOWLP)/Fan-Out Panel-Level Packaging (FOPLP) są formowane na strukturach scalonych w ramach jeszcze niepodzielonej płytki półprzewodnikowej, a dopiero potem następuje wyodrębnienie poszczególnych układów. Zasadnicza różnica pomiędzy nimi dotyczy sposobu włączenia do opakowania warstwy redystrybucyjnej, w której prowadzi się połączenia wyprowadzeń struktury scalonej z wyprowadzeniami obudowy układu scalonego.

W obudowach FIWLP pokrywa się ona z obrysem struktury scalonej. Ten typ opakowań sprawdza się w przypadku stosunkowo małej liczby wyprowadzeń. W obudowach FOWLP/FOPLP strukturę scaloną osadza się w materiale podłoża z zapasem miejsca na warstwę redystrybucyjną. Sprawdzają się, gdy wymagany jest większy poziom integracji na mniejszej powierzchni oraz większa liczba wyprowadzeń. Mają też lepsze parametry termiczne i elektryczne niż obudowy FIWLP.

Technologie pakowania 2,5D i 3D

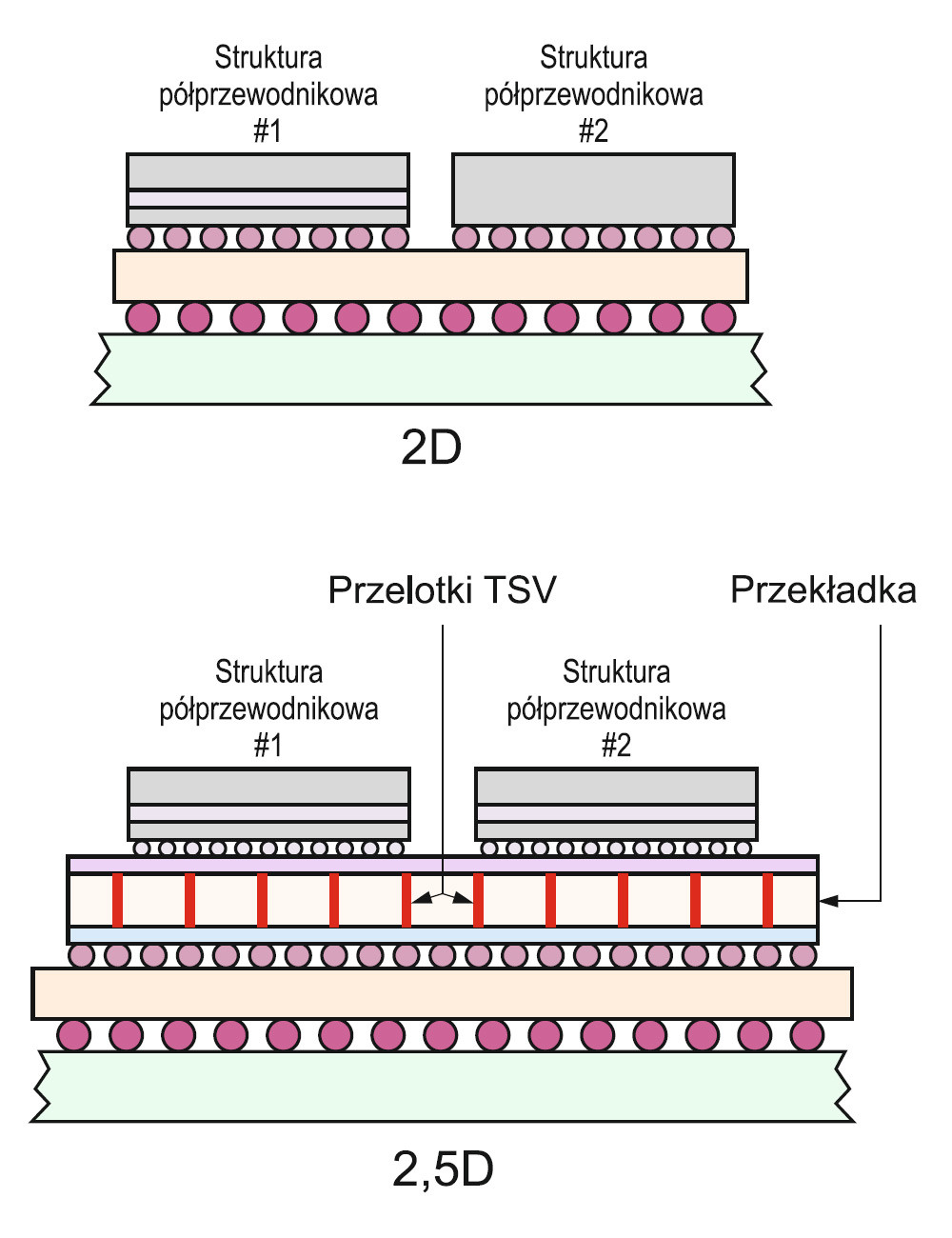

Obudowy FOWLP, które zaczęły się upowszechniać po 2010 roku, zapoczątkowały ewolucję w kierunku konstrukcji 2,5D i 3D, które uznaje się za kolejne kroki milowe w historii technologii pakowania układów scalonych. Nim je przedstawimy, warto jest przypomnieć, jak rozwijały się technologie pakowania 2D.

W początkach lat 90. zeszłego wieku upowszechniły się obudowy MCM (Multi-Chip Modules). Mieściły one kilka układów scalonych połączonych w technice wirebonding z PCB, a cała konstrukcja była zabezpieczona obudową z tworzywa sztucznego lub ceramiki. Kolejnym etapem były układy SoC (System-on-Chip), w których bloki funkcyjne są wykonywane w obrębie jednej struktury scalonej. Pozwala to w dużym stopniu ją zoptymalizować. Równocześnie proces jej projektowania jest czaso- i pracochłonny, zaś w przypadku rozszerzenia funkcjonalności wymagane jest jej ponownego przeprojektowanie.

Około roku 2000, można powiedzieć, historia zatoczyła koło i znów na popularności zyskały układy MCM, tym razem jednak określane skrótem SiP (System-in-Package). Tego typu konstrukcje, składające się z wielu układów scalonych zamkniętych w jednej obudowie i dzięki temu tworzących kompletny w pełni funkcjonalny system, można łączyć po kilka w jednym większym układzie SiP, tworząc PiP (Package-in-Package) albo umieszczać jeden SiP na drugim w ramach PoP (Package-on-Package).

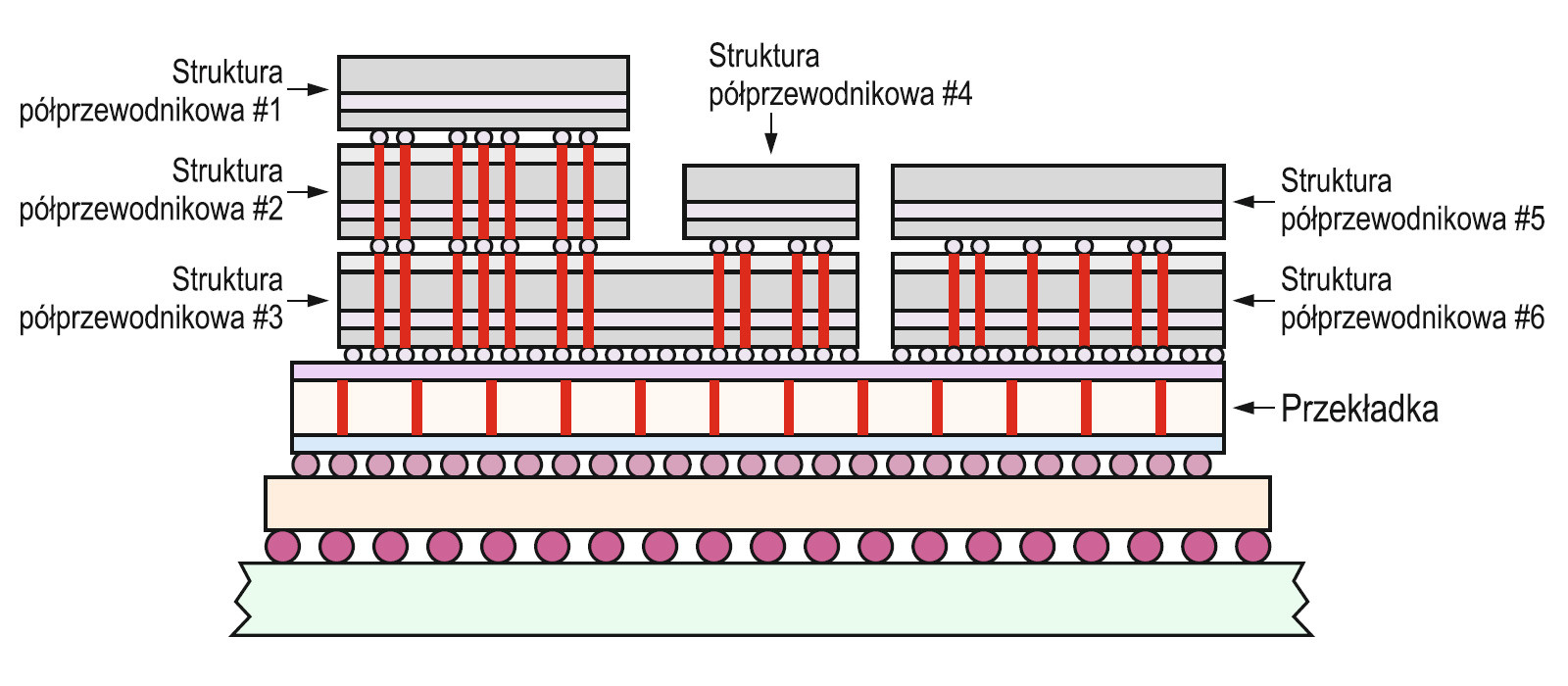

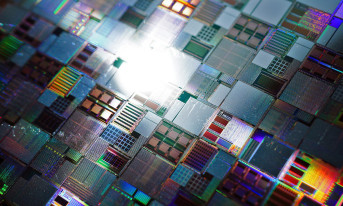

Wszystkie wymienione dotychczas rozwiązania zalicza się do kategorii 2D. Zasadnicza różnica między nimi a wersją 2,5D polega na tym, że między podłożem a strukturami półprzewodnikowymi umieszczono przekładkę (interposer), krzemową lub z materiału organicznego, z przelotkami TSV (Through-Silicon Vias). Jeżeli za pośrednictwem przekładek oraz TSV struktury półprzewodnikowe są umieszczane jedna na drugiej, mamy z kolei do czynienia z konstrukcjami 3D.

Podsumowanie

Zadaniem producentów elektroniki jest szukanie sposobów na ominięcie ograniczeń, które na postęp w przemyśle półprzewodników nakłada prawo Moore'a. W tym celu przez lata rozwijano procesy produkcyjne struktur scalonych. W miarę jednak jak postępowała miniaturyzacja, okazało się, że to już nie wystarczy i – czego dowodzi przedstawiony przegląd technik pakowania – obudowy układu scalonego nie powinno się rozpatrywać niezależnie, lecz należy ją traktować jak integralną część podzespołu, w tym zakresie też wprowadzając innowacje. Ukoronowaniem tych wysiłków zdaje się być technika pakowania 3D.

W jej przypadku, wzorowano się na podejściu stosowanym w budownictwie, w którym, jeżeli zaczyna brakować miejsca w poziomie, poszukuje się go w pionie, budując wieżowce. Analogicznie, gdy koszty rozwoju i ograniczenia skalowania technologii krzemowej nie pozwalają już na miniaturyzację przez zmniejszanie wymiaru charakterystycznego procesu, a jednocześnie rynek napędza popyt na lekkie i kompaktowe elementy elektroniczne, struktury trójwymiarowe wydają się najbardziej przyszłościowym rozwiązaniem.

Monika Jaworowska