Realizację projektu rozpoczyna się najczęściej od schematu elektrycznego. Warto zadbać o jego właściwe opracowanie, aby proces projektowania PCB był jak najbardziej ułatwiony. Jedną z technik jest umieszczanie oznaczeń i dyrektyw, które na dalszym etapie będą stanowiły jasną wskazówkę, jak projektować poszczególne moduły obwodu.

Realizację projektu rozpoczyna się najczęściej od schematu elektrycznego. Warto zadbać o jego właściwe opracowanie, aby proces projektowania PCB był jak najbardziej ułatwiony. Jedną z technik jest umieszczanie oznaczeń i dyrektyw, które na dalszym etapie będą stanowiły jasną wskazówkę, jak projektować poszczególne moduły obwodu.

Przykładem może być oznaczanie par różnicowych i właściwe ich nazywanie, aby w edytorze PCB można było łatwo je wychwycić i zastosować odpowiedni sposób trasowania. Niektóre pakiety EDA dzięki znacznikom (dyrektywy, etykiety, etc.) są w stanie rozpoznać sygnały różnicowe i pozwalają przypisywać odpowiednie reguły projektowe odpowiedzialne za nadzór nad zachowaniem ich właściwych parametrów.

Kolejnym aspektem wartym odnotowania na schemacie są ścieżki wysokoprądowe, grupy połączeń z koniecznym wyrównaniem długości ścieżek, elementy wymagające radiatora, ścieżki o określonej impedancji charakterystycznej, czy punkty łączenia mas. Zmniejszy to liczbę błędów w projekcie, szczególnie, gdy za projektowanie PCB odpowiada inny zespół.

Przystępując do pracy nad płytką drukowaną, pierwszą, najbardziej oczywistą czynnością będzie zdecydowanie ile warstw ma mieć obwód drukowany. Liczba ta zawsze stanowi kompromis między:

- szybkością projektowania - większa liczba warstw pozwala rozłożyć krzyżujące się połączenia na poszczególnych płaszczyznach, dzięki czemu projektant mniej czasu poświęca na rozlokowanie ścieżek,

- ceną - wzrost liczby warstw pociąga za sobą wzrost kosztów wytworzenia dokumentacji produkcyjnej oraz samych obwodów,

- integralnością sygnałów - większa liczba warstw pozwala dodawać plany zasilania, plany masy i prowadzić ścieżki z pełniejszą kontrolą impedancji.

Liczba warstw nie zawsze może zostać obniżona poniżej pewnego poziomu w złożonych projektach, nawet gdy pominie się dłuższy czas projektowania i związane z tym koszty. Spowodowałoby to pogorszenie parametrów elektrycznych do tego stopnia, że będę one nieakceptowalne i przełożą się na nieprawidłową bądź niestabilną pracę urządzenia.

W przypadku prostych urządzeń zawierających jedynie niewielkie mikrokontrolery obwód drukowany może zostać zaprojektowany na płytce jedno- bądź dwuwarstwowej. Obwody bardziej złożone, wyposażone w zaawansowane podzespoły cyfrowe, takie jak pamięci DDR2/DDR3, układy programowalne czy procesory sygnałowe są praktycznie niemożliwe do zaprojektowania na płytkach liczących mniej niż cztery warstwy. Niestety, zbyt małą ilością może okazać się również 6 czy 8 warstw.

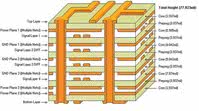

Współczesne komponenty, umieszczone w obudowach BGA liczących setki wyprowadzeń wymagają najczęściej kilku warstw jako punkt wyjścia. Warstwy sygnałowe i plany masy oraz zasilania układa się w tzw. stos (stack layer) - rysunek 1. Ułożenie i liczba planów masy i zasilania decyduje o aspektach takich jak: impedancja charakterystyczna ścieżek, właściwości elektromagnetyczne urządzenia (EMI), jakość zasilania, itd.

Przed przystąpieniem do projektu opartego o zaawansowane i złożone układy cyfrowe należy mieć na uwadze szereg wymagań do spełnienia, aby zagwarantować ich poprawną pracę. Dobrym punktem wyjścia do poznania tych wymagań są udostępniane przez producentów noty aplikacyjne wskazujące rzeczy najbardziej istotne.

Mogą to być pojemności kondensatorów odsprzęgających, dopuszczalne tolerancje długości ścieżek, sposób wykonania terminacji połączeń, impedancja charakterystyczna połączeń, itd. Spotkać można również gotowe listy kontrolne, na których wyszczególniono krok po kroku jak zweryfikować projekt obwodu, aby mieć jak największą pewność, że będzie on działał poprawnie.

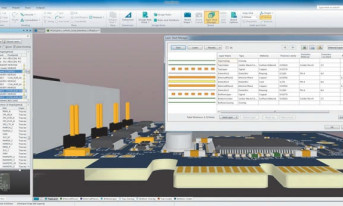

Pomocne są profesjonalne, komercyjne pakiety EDA zawierające wbudowane moduły symulacji obwodów drukowanych oraz szereg narzędzi usprawniających proces projektowania z dbałością o parametry elektryczne połączeń. Potrafią one ostrzegać o problemach z integralnością sygnałów, czy też z przesłuchami między ścieżkami. Są to rozwiązania warte poznania, gdyż mogą uchronić od oczywistych błędów i zmuszą do weryfikacji potencjalnie problematycznych połączeń.

Projekt warto przemyśleć także w aspekcie mechanicznym. Nie chodzi tu tylko o umiejscowienie złączy, przystosowanie do montażu seryjnego, ale również o kwestie takie jak stałe zagęszczenia miedzi na całym obszarze płytki. Ma to znaczenie zwłaszcza dla płytek o dużych powierzchniach, gdyż ogranicza powstawanie wypaczeń gotowej płytki, zwłaszcza, po osadzeniu na niej ciężkich elementów.

Stałe zagęszczenie sprowadza się do zastępowania pustych obszarów PCB planem masy bądź zasilania (w formie jednolitej, siatki czy punktów). Dobrą praktyką będzie zweryfikowanie np. za pomocą narzędzi do symulacji, czy wprowadzone w ten sposób zmiany nie wpłyną na pogorszenie właściwości elektrycznych i elektromagnetycznych układu.

Zasilanie

Kluczową sprawę stanowi zasilanie, które jest pośrednio zależne od sposobu ułożenia warstw. W obwodach jedno i dwuwarstwowych zasilanie najczęściej jest rozprowadzane w formie ścieżek. Im są one dłuższe i cieńsze, tym ich rezystancja jest większa. Problem zaczyna się, gdy pobór prądu ma charakter impulsowy, co często ma miejsce we współczesnych układach cyfrowych.

Kluczową sprawę stanowi zasilanie, które jest pośrednio zależne od sposobu ułożenia warstw. W obwodach jedno i dwuwarstwowych zasilanie najczęściej jest rozprowadzane w formie ścieżek. Im są one dłuższe i cieńsze, tym ich rezystancja jest większa. Problem zaczyna się, gdy pobór prądu ma charakter impulsowy, co często ma miejsce we współczesnych układach cyfrowych.

Chwilowe zapotrzebowanie na prąd, które w momencie przełączania jest stosunkowo wysokie, nie zawsze może zostać zaspokojone. Spadki napięcia powstałe wskutek zwiększonej impedancja ścieżek obniżają napięcie zasilania układów cyfrowych przez co może ono być za niskie. Przeciwdziałać temu zjawisku można stosując jednolite plany masy oraz zasilania. Ze swej natury gwarantują one ścieżkę zarówno "najgrubszą" i "najkrótszą", co zmniejsza pasożytniczą impedancję do minimum.

Dążąc do zapewnienia właściwej dystrybucji energii nie można zapominać, że gęstość rozmieszczenia przelotek musi być adekwatna do płynącego przez nie prądu. Pojedyncza przelotka w skutek nadmiernego obciążenia prądowego ulegnie uszkodzeniu, więc tylko odpowiednia ich liczba umieszczona obok siebie pozwoli uniknąć problemów. Dodatkową zaletą takiego podejścia jest zmniejszenie impedancji i poprawa jakość zasilania podzespołów.

Starannym i przemyślanym rozmieszczanie przelotek można ułatwić sobie pomiary oscyloskopem na etapie uruchamiania projektu. Przelotki umożliwiają przyłożenia sondy do ścieżek biegnących po wewnętrznych warstwach. Stopień zaszumienia pomiaru i jego jakość zależą w znacznej mierze od bliskości punktu masy podłączonej do oscyloskopu.

Zbyt duża odległość może utrudnić ocenę parametrów sygnału, więc warto dbać o dostępność lokalnej masy tam, gdzie planuje się prowadzenie pomiarów. Kolejnym ułatwieniem będą opisy przelotek umieszczone na warstwie opisowej płytki drukowanej. Pozwoli to szybko zlokalizować punkt przyłożenia sondy bez zaglądania w dokumentację.

Plan masy jest kluczowy, gdy w układzie występują sygnały wysokiej częstotliwości, wymagany jest niski poziom szumów własnych, czy odporność na zaburzenia elektromagnetyczne. Płaszczyzna masy skraca ścieżki powrotne prądu i dodatkowo ekranuje połączenia na innych warstwach. Dzieląc płaszczyzną masy można wyodrębnić poszczególne bloki funkcjonalne, co pozwoli dodatkowo poprawić jakość zasilania w obszarach szczególnie wrażliwych, zmniejszyć zaburzenia elektromagnetyczne przedostające się do wrażliwych miejsc układu, takich jak obwody analogowe, zasilanie wrażliwych komponentów elektronicznych, czy wysokoczuły odbiorników sygnału.

Omawiając zagadnienia związane z zasilaniem nie sposób nie wspomnieć o problemach związanych z rozpraszaniem ciepła. Elementy w obudowach SMD emitujące duże ilości ciepła wymagają starannego przemyślenia kwestii jego odprowadzania. Najprostszą metodą pozostaje pozostawienie odpowiednio dużego padu, który odbierze to ciepło i przekaże do otoczenia.

Nie zawsze jest to jednakże możliwe, więc warto pamiętać o wykonaniu przelotek, które również odbiorą cześć energii cieplnej i przeniosą ją do planu masy bądź zasilania. Warto dążyć do zwiększania liczby przelotek w takich miejscach, aby poprawić jakość chłodzenia i zapobiec odparzeniu viasów.

Odsprzęganie zasilania

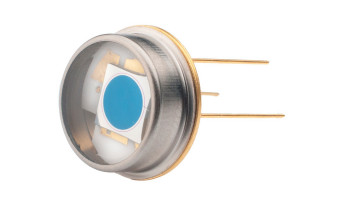

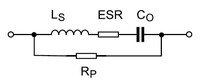

Rys. 2. Model kondensatora pracującego przy wysokiej częstotliwości: LS - ekwiwalentna indukcyjność szeregowa, RP- rezystancja równoległa, ESR - ekwiwalentna rezystancja szeregowa, CO - pojemność nominalna

Podstawową zasadą podczas rozmieszczania kondensatorów odsprzęgających jest maksymalne skracanie połączenia między takim kondensatorem a pinem zasilania układu. Pasożytnicza indukcyjność ulegnie dzięki temu zredukowaniu i poprawi się skuteczność filtrowania zakłóceń. Teoretycznie elementy te spełniają funkcję filtru pojemnościowego zwierającego do masy harmoniczne o częstotliwości większej niż 1/(2πfC).

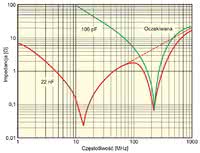

Mogłoby się wydawać, że zwiększanie pojemności spowoduje zwiększenie skuteczności odsprzęgania. W praktyce jednak tak nie jest i stosuje się kondensatory rzędu nanofaradów ze względu na mniejsza indukcyjność pasożytniczą, która ma kluczowe znaczenie dla pracy w wyższej częstotliwości. Na rysunku 2 pokazano rzeczywisty model zastępczy kondensatora dla wysokich częstotliwości.

Obecności takiego "rzeczywistego" elementu powoduje powstanie filtru rezonansowego. Harmoniczne przekraczające częstotliwość rezonansową nie będą zwierane do masy - impedancja będzie rosła w funkcji częstotliwości. Zachowanie to zobrazowano wykresem na rysunku 3. Chcąc uzyskać pokrycie możliwie szerokiego pasma filtrowanych zakłóceń stosuje się kilka kondensatorów o różnej pojemności połączonych równolegle.

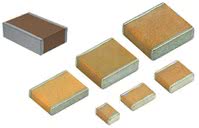

Jest to szczególnie ważne w obwodach cyfrowych pracujących z sygnałami o wysokich częstotliwościach. Dąży się także do obniżenia pasożytniczej indukcyjności do minimum umieszczając przelotki wewnątrz padów bądź dodając je po obu stronach kondensatora. Dalsze zmniejszenie indukcyjności można osiągnąć stosując kondensatorów o specjalnej konstrukcji - posiadające wyprowadzeniami na dłuższych bokach (np. 0204 zamiast 0402 - rys. 4).

Elementy w obudowach typu "X2Y" oferuje kilku producentów, jednak warte są zainteresowania ze względu na znacznie lepsze zachowanie w obszarze wysokich częstotliwości. Warto dążyć do umieszczania kondensatorów jak najbliżej planów masy i zasilania - im dłuższa przelotka, tym większa indukcyjność pasożytnicza.

Warto zauważyć, że plan masy i zasilania może zachowywać się jak okładziny kondensatora i wprowadzać własną pojemność do układu i stanowić dodatkowy element odsprzęgania zasilania. Korzystne jest zwiększanie tej pojemności, co można osiągnąć poprzez zmniejszanie odległości między warstwą zasilania i masy. Wynika to bezpośrednio ze wzoru na pojemność, która jest wprost proporcjonalna do powierzchni okładzin i odwrotnie proporcjonalna do odległości między nimi.

Produkcja

Rys. 4. Zmniejszenie indukcyjności pasożytniczych można osiągnąć stosując kondensatorów o specjalnej konstrukcji - posiadające wyprowadzeniami na dłuższych bokach, np. w rozmiarach 0204, 0306, 0508, 0612

Wytworzenie fizycznych obwodów drukowanych jest najczęściej zlecane firmom zewnętrznym. Jeżeli cena jest kluczowa, to warto decydować się na konkretnego dostawcę jeszcze przed rozpoczęciem projektowania PCB. Pozwoli to ocenić jak sposób projektowania wpłynie na całkowity koszt produkcji. Wybór technologii i liczby warstw ma znaczący wpływ na cenę jednostkowej płytki, a także cenę końcowego produktu.

Odnosi się to zwłaszcza do produkcji układów w małych seriach lub prototypów. Koszt wytworzenia dokumentacji technicznej niezbędnej do uruchomienia produkcji bywa liczony w tysiącach złotych. Cenę dodatkowo podnosi używanie przelotek zagrzebanych i ślepych, stosowanie małych otworów pod przelotki (rzędu 0,1 mm - wymagają one wycinania laserem) i zwiększanie liczby warstw.

Firmy produkcyjne często podają wytyczne niezbędne dla prawidłowego przebiegu procesu produkcji. Zatrudniają wyspecjalizowanych inżynierów, więc warto wyjaśniać wątpliwości już na etapie tworzenia projektu. Jest to szczególnie wskazane podczas projektowania obwodów drukowanych wymagających bardzo restrykcyjnej kontroli parametrów. Producent najczęściej wprowadzi pewne modyfikacje do projektu, aby skompensować wpływ procesu technologicznego na impedancję ścieżek.

Kontrola impedancji

Rys. 5. Rozbudowane narzędzie Saturn PCB Design Toolkit umożliwiające wyliczenie wielu użytecznych parametrów takich jak impedancja ścieżek, impedancja przelotek i wiele innych

Kontroli impedancji wymagają układy przeznaczone do pracy z sygnałami o wysokich częstotliwości - rzędu setek megaherców. Dopasowanie impedancyjne między nadajnikiem, a odbiornikiem pozwala uzyskać sygnał o najlepszych parametrach elektrycznych. Proces kontroli impedancji rozpoczyna się już na etapie wyboru liczby warstw w obwodzie drukowanym.

Pierwszy krok stanowi ustalenie, jak mają być rozmieszczone plany zasilania oraz warstwy sygnałowe względem siebie, co ma niebagatelne znaczenie dla utrzymania prawidłowej impedancji ścieżek. W idealnym przypadku płaszczyzny masy powinny być znacznie większe niż obszar zajmowany przez ścieżki. Zawsze gdy jest to możliwe, należy unikać dzielenia płaszczyzny masy na sekcje. Niejednolitość planu masy na skutek powstałych przerw sprawi, że ścieżki będą miały pogorszone parametry elektrycznych. Rozwiązaniem tego problemu może być dołożenie kolejnej warstwy masy, ale nie zawsze jest możliwe z ekonomicznego punktu widzenia.

O wartości impedancji, poza ułożeniem warstw w stosie, decydują: odległości między ścieżkami (zwłaszcza dla par różnicowych), grubość ścieżek, grubość warstwy miedzi i odległość między warstwami. Warto zauważyć, że wykonując zaawansowane obwody drukowane należy poinformować producenta o pożądanych odległościach pomiędzy warstwami i oczekiwanej grubości miedzi.

Nie zawsze producent jest w stanie zagwarantować pełną elastyczność w tej kwestii. Pozostaje wtedy zaakceptować wartości odgórnie narzucone oraz dobrać grubości ścieżek i/lub odległość między nimi. Współczesne narzędzia EDA usprawniają proces kontroli impedancji poprzez udostępnienie wygodnych kreatorów samodzielnie dobierających potrzebne parametry. Prostsze narzędzia do projektowania PCB są pozbawione takich udogodnień, lecz na szczęście dostępne są aplikacje zewnętrzne.

Przykładem niech będzie rozbudowane narzędzie Saturn PCB Design Toolkit umożliwiające wyliczenie wielu użytecznych parametrów takich jak impedancja ścieżek, impedancja przelotek i wiele innych (rys. 5). Na podstawie wprowadzonych danych obliczana jest wybrana wartość. Przykładowe wyliczenia pokazano na rysunku 5. Wprowadzając odległości między ścieżkami, ich grubość, sposób umieszczenia względem planów masy, aplikacja podaje impedancję tych połączeń.

Dysponując oprogramowaniem do symulacji impedancji połączeń warto poświęcić trochę czasu na "zabawę" nim. Obserwowanie wpływu geometrii ścieżek, ich ułożenia oraz odległości pozwoli uzmysłowić sobie jak zmienia się impedancja w funkcji tych parametrów. Pozyskane w ten sposób doświadczenie przełoży się z czasem na lepsze zrozumienie problemu impedancji i w efekcie skróci czas projektowania.

Warto pamiętać, że umieszczanie przelotek na ścieżkach objętych kontrolą impedancji może pogarszać ich właściwości elektryczne. W miarę możliwości warto unikać przelotek, a gdy nie będzie to możliwe - wyliczyć parametry przelotki, aby zminimalizować jej wpływ na impedancję połączenia. Stosowanie przelotek ślepych bądź zagrzebanych potrafi znacząco podnieść koszty związane z produkcją obwodów drukowanych, jednak pozwala to dodatkowo poprawić parametry elektryczne. Jeżeli z przejściem sygnału przez przelotkę wiąże się zmiana płaszczyzny masy stanowiącej punkt odniesienia, to warto w sąsiedztwie umieścić przelotki przewodzące masę. Jeżeli jedną z płaszczyzn odniesienia będzie plan zasilania, korzystne jest umieszczenie w pobliżu kondensatora odsprzęgającego.

Kontrola długości połączeń

Rys. 6. Wyrównanie długości połączeń osiąga się poprzez skracanie ścieżek do długości najkrótszej z domeny zegarowej lub poprzez wydłużanie najkrótszych. Współczesne środowiska projektowe mają narzędzia wspomagające ten proces - powyżej pokazano narzędzie dostępne w Altium Designer

Dążąc do zapewnienia jak najlepszej integralności sygnałów nie można zapomnieć o wyrównywaniu długości ścieżek sygnałowych. Problem ten narasta wraz ze wzrostem częstotliwości sygnału zegarowego. Propagacja sygnału elektrycznego nie jest nieskończenie krótka i różnica w długości ścieżek w obrębie danej domeny zegarowej sprawi, że dane będą przesunięte względem zbocza sygnału zegarowego.

Zjawisko to wymusza na projektantach utrzymywanie długości połączeń na stałym poziomie, w ramach dopuszczalnej tolerancji. Przekroczenie dopuszczalnej tolerancji sprawi, że sygnał nie będzie stabilny w chwili wystąpienia zbocza zegarowego (zatrzaskiwania danych). Tym samym warto zadbać, aby ścieżka prowadząca sygnał zegarowy nie była krótsza niż najdłuższa ze ścieżek danych.

Wyrównanie długości połączeń osiąga się poprzez skracanie ścieżek do długości najkrótszej z domeny zegarowej lub poprzez wydłużanie najkrótszych. W praktyce najczęściej konieczne jest wydłużanie ścieżek. Współczesne środowiska projektowe mają narzędzia wspomagające ten proces (rys. 6 - narzędzie dostępne w Altium Designer).

Umożliwiają one płynne zwiększanie długości, tak aby osiągnąć założoną wartość. Komplikacje na tym etapie powstają z powierzchni zajmowanej przez tak wydłużane ścieżki - nie zawsze jest dostępne wolne miejsce. W praktyce konieczne może się okazać odsuwanie innych połączeń leżących w pobliżu. Warto przemyśleć rozmieszczenie połączeń na dostępnych warstwach obwodu drukowanego, aby ograniczyć krzyżowanie i uzyskać możliwie krótkie ścieżki. W tym miejscu jeszcze raz należy podkreślić znaczenie wyboru liczby warstw w projekcie. Im ich liczba jest większa, tym łatwiej kontrolować długość połączeń, gdyż w razie potrzeby można je przenosić między warstwami.

Prowadząc pary różnicowe warto dążyć do prowadzenia ich prosto, gdyż zapewnia to równą długość każdej ścieżki w parze. W sytuacji, gdy powyższy warunek nie jest dotrzymany wystąpi różnica długości obu ścieżek i niezbędne będzie zadbanie o ich wyrównanie poprzez skręt w przeciwnym kierunku lub wydłużenie jednej ze ścieżek. Dopuszczalny jest zazwyczaj pewien margines niezrównoważenia ścieżek pary różnicowej, jednak należy pilnować, aby go nie przekroczyć. Niezachowanie tego warunku skutkuje różnymi czasami propagacji sygnału w obu liniach pary różnicowej, w efekcie czego będą przesunięte między sobą (skew).

Interferencje elektromagnetyczne

Projektując obwody drukowane nie można zapominać o interferencjach elektromagnetycznych (EMI), które stają się szczególnie problematyczne, gdy urządzenie operuje sygnałami wysokiej częstotliwości. Podstawowy problem stanowi emisja zaburzeń elektromagnetycznych do otoczenia, przez co urządzenie może nie spełniać wymogów kompatybilności elektromagnetycznej.

Szczególnie wrażliwe pod tym względem są złącza przewidziane do komunikacji z urządzeniami zewnętrznymi. Związane z nimi połączenia przewodowe stanowią naturalną antenę emitujące fale elektromagnetyczne do otoczenia. Ekranowanie obudowy złączy pozwala ograniczyć szkodliwe zjawiska, nie zawsze jednak pożądane jest łączenie metalowych elementów bezpośrednio do masy. Pozostaje rozważenie połączenia z masą poprzez rezystor, kondensator bądź ich równoległe połączenie, co również przynosi poprawę. Pomocne okazują się zabezpieczenia umieszczane na przewodach takie jak koraliki ferrytowe, dławiki.

Przemyślany projekt PCB przyczynia się do zmniejszenia emisyjności. Można to osiągnąć umieszczając ścieżki przewodzące sygnały szybkozmienne na wewnętrznych warstwach obwodu drukowanego lub pomiędzy planami masy. Zwiększeniu ulega przy okazji odporność samego obwodu na zewnętrzne zaburzenia elektromagnetyczne.

Sytuacja nie jest tak komfortowa przy projektowaniu obwodów jedno- oraz dwustronnych, ale pozostaje możliwość prowadzenia wrażliwych połączeń między ścieżkami masy. Pamiętać należy o weryfikacji i ewentualnej kompensacji impedancji takich połączeń, gdyż prowadzone w pobliżu ścieżki masy mogą ją zmienić. Opracowując obwody z krytycznym wpływem impedancji połączeń na działanie układu pozostaje przewidzieć ścieżki testowe pozwalające zmierzyć rzeczywistą impedancję na wyprodukowanej płytce drukowanej. Łatwiej wtedy zweryfikować zgodność projektu z rzeczywistością.

Podsumowanie

Zaprojektowanie złożonego obwodów drukowanych dla szybkich układów cyfrowych w sposób prawidłowy nie jest rzeczą łatwą. Dodatkowym utrudnieniem jest konieczność spełniania rygorystycznych norm stawianych przez europejskie prawodawstwo. Istnieje szereg zaleceń i dobrych praktyk opisanych w literaturze czy też notach aplikacyjnych, przestrzeganie których znacząco zwiększa szansę powodzenia i pozwoli uniknąć wielu pułapek.

Warto poświęcić czas na przeanalizowanie materiałów dostarczanych przez producentów układów scalonych, gdyż mając za sobą szereg przeprowadzonych badań i wykwalifikowanych inżynierów potrafią najlepiej doradzić, jak uniknąć problemów. Bezcenne jest doświadczenie i praktyka, gdyż to one pozwalają szybko i skutecznie wychwycić potencjalne problemy i zaradzić im na samym początku, zanim obwód zostanie przekazany do wykonawcy. Brak doświadczenia, spotykany np. u młodszych projektantów, warto kompensować narzędziami wspomagającymi projektowanie, gdyż są one w stanie ustrzec przed częścią błędów i pomogą ocenić szanse na prawidłowe zakończenie etapu projektowania.

Jakub Borzdyński