Według źródeł branżowych cytowanych przez koreańskie media ChosunBiz, Samsung osiągnął lepsze niż oczekiwano wyniki w zakresie rozwoju technologii BSPDN - zmniejszono powierzchnię chipów, jednocześnie zwiększając wydajność i efektywność.

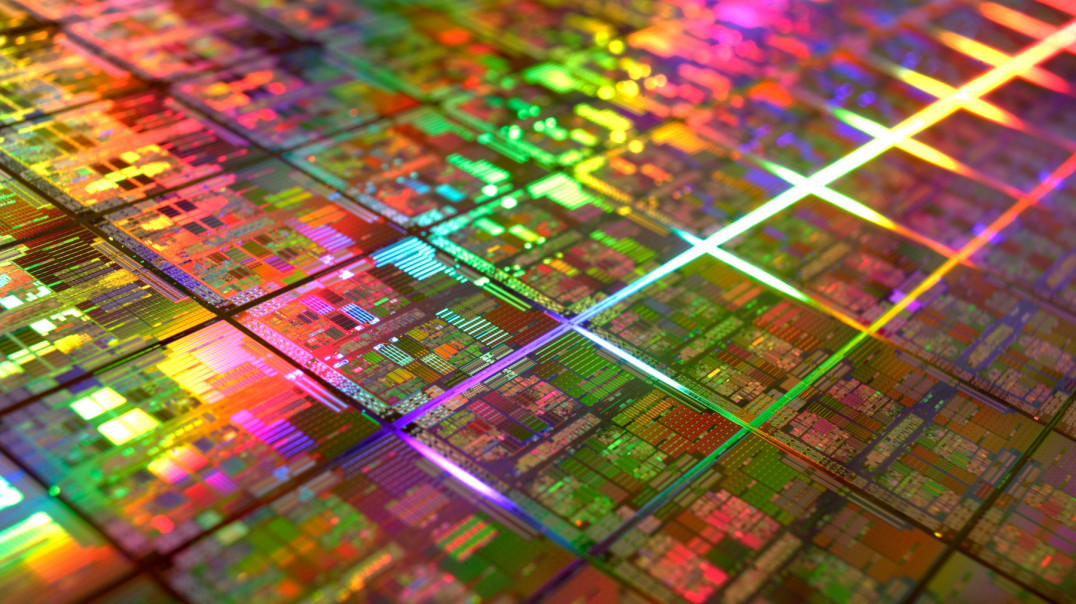

Tradycyjnie projektanci chipów umieszczają linie zasilające na przedniej stronie płytki, aby ułatwić proces produkcyjny. Jednakże w miarę jak obwody stają się coraz bardziej skomplikowane, umieszczanie obwodów i linii zasilających po jednej stronie staje się trudne. Ponadto malejące przerwy między obwodami mogą prowadzić do zakłóceń elektrycznych, co jeszcze bardziej komplikuje projektowanie i produkcję chipów.

W związku z tym BSPDN jawi się jako przełamanie tych ograniczeń. Dzięki liniom zasilającym umieszczonym z tyłu płytki, BSPDN oddziela przestrzeń dla skomplikowanych obwodów od dostarczania mocy, maksymalizując w ten sposób efektywność energetyczną i poprawiając wydajność chipa. Technologia ta może również skutecznie zmniejszyć powierzchnię chipa, ułatwiając dalszą miniaturyzację procesorów aplikacji mobilnych (AP).

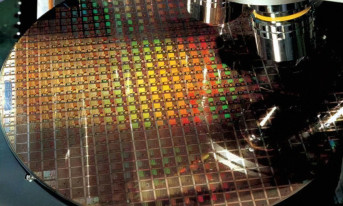

Samsung - wspierany przez rozwój BSPDN przekraczający oczekiwania - jest na dobrej drodze do przyspieszenia komercjalizacji w stosunku do pierwotnego terminu określanego na rok 2027. Wstępne raporty wskazywały, że Samsung wdroży technologię BSPDN w procesie 1,7 nm, ale najnowsze doniesienia sugerują wcześniejszą integrację z procesem 2 nm do 2025 r.

Mimo że Samsung robi postępy w rozwoju BSPDN, obecnie uważa się, że to Intel jest liderem w tej dziedzinie. Celem Intela jest rozpoczęcie masowej produkcji z wykorzystaniem technologii BSPDN w 2024 r., przy czym nastąpić ma integracja z chipami wytwarzanymi w procesie 20A (2 nm). Intel stworzył nawet markę "PowerVia", by podkreślić swoje możliwości w zakresie BSPDN. Tymczasem TSMC planuje włączyć technologię BSPDN do swojego procesu o wymiarze charakterystycznym poniżej 2 nm.

Źródło: DigiTimes