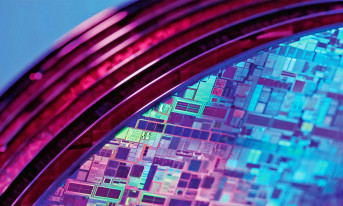

Połączenia sygnałowe muszą być jak najkrótsze i jeśli całość mieści się w chipie, to jest to optymalne rozwiązanie. Jednym ze sposobów zwiększania stopnia upakowania w obszarze technologii półprzewodnikowej jest tzw. integracja homogeniczna, której przykładem są chipy SoC. W nich na jednej monolitycznej strukturze umieszcza się procesor, pamięć, interfejs komunikacyjny itd., składając z komponentów logicznych (bloków IP) cały system.

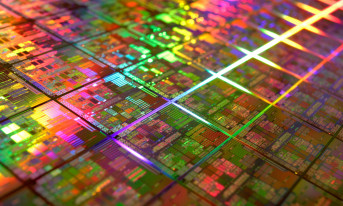

Tak wytwarza się dzisiaj mnóstwo zaawansowanych układów scalonych, ale coraz częściej słychać opinie, że SoCe się już kończą, bo cały czas są one jedną płaską i dużą strukturą. Ich producenci mają problemy z uzyskiem, a poza tym dochodzą inne kłopoty, jak chociażby to, że nie dają możliwości łączenia różnych technologii półprzewodnikowych oraz integracji gotowych produktów różnych dostawców.

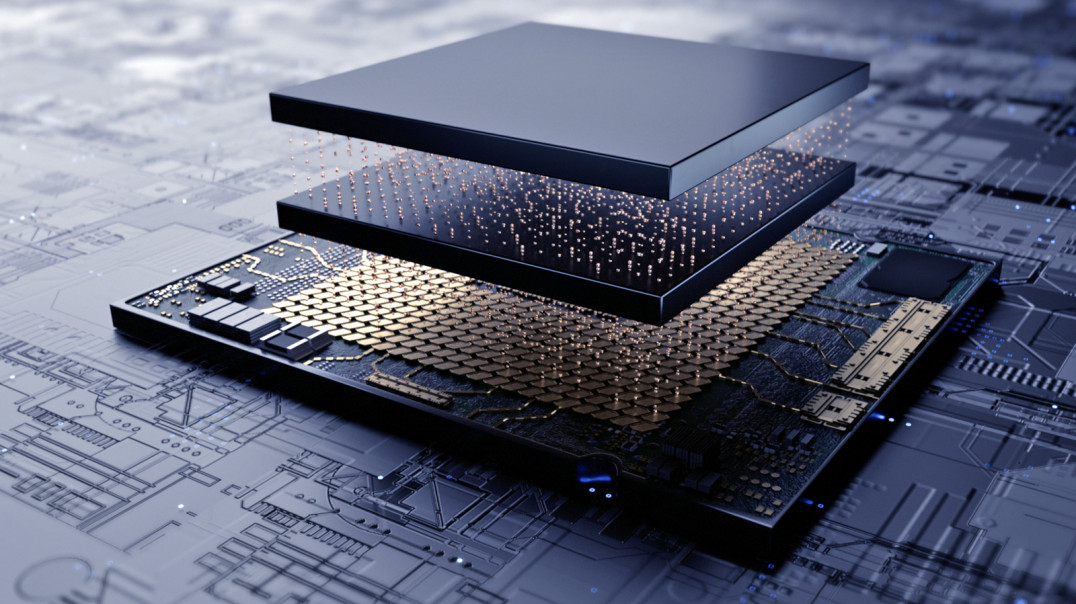

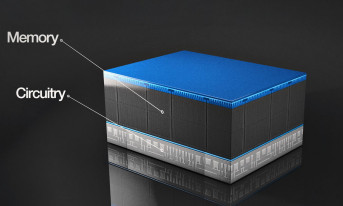

Miniaturyzacja nowoczesnych platform półprzewodnikowych wymusza to, by w jednej obudowie był procesor, duża pamięć, czujniki oraz inne bloki funkcjonalne. Aby to wszystko pomieścić bez zajmowania dodatkowej powierzchni na PCB, konieczna stała się rozbudowa w pionie, a więc zmiana modelu produkcji na układy scalone trójwymiarowe (3D IC). Różnią się one tym od znanych rozwiązań SiP (System in Package), że nie tylko nie są płaskie, ale też nie bazują na połączeniach za pomocą drutu (poprzez bonding), jak było w przypadku rozwiązań MCM znanych już w latach 70. ubiegłego wieku. Wracamy do dawnych pomysłów, bo przelotki przez strukturę oraz warstwy podłożowe (interposer), na których są one mocowane, dają nowe możliwości. Poza mechaniczną stabilizacją podłoża rozprowadzają sygnały między strukturami oraz tworzą pola do kontaktów kulkowych, jak w obudowach BGA.

Układy 3D pozwalają na łączenie różnych technologii, produktów gotowych, które kupuje się w wersjach nieobudowanych (np. czujników MEMS), z blokami IP własnymi i kupionymi na rynku. To tzw. integracja heterogeniczna, a więc bardzo różnorodna i bez wielu ograniczeń technologicznych. Razem z chipami na podłożu montowane są elementy pasywne, zarówno dyskretne, jak i wersje zintegrowane, np. kompletne sieci filtrów, układy dopasowujące antenę, cewki planarne. One też trafiają do wnętrza obudów. Taki sposób zapewnia większy uzysk produkcyjny, bo jak wiadomo, duże struktury mają z tym problem.

Skomplikowanie technologii półprzewodnikowej bardzo szybko się zwiększa, tak samo jak liczba pojawiających się innowacji i równoważnych funkcjonalnie rozwiązań. Wywołuje to większą presję na współpracę między producentami i zespołami projektantów z różnych firm, stąd możliwość kompozycji układu scalonego w oparciu nie tylko o własne struktury, jest dzisiaj już bardzo powszechna.

Pionowe elementy są łączone za pomocą przelotek przez krzem TSV, kontakty z interposerem za pomocą kulek, jak w BGA, a np. MEMS-y za pomocą bondingu. Magistrale połączeń (redistribution layers, RDL) wykonuje się z użyciem miedzianych ścieżek na podłożu interposera. Ogólnie schematy ułożenia takich struktur są skomplikowane, a rozbudowa wcale nie jest realizowana jedynie do góry.

Wydaje się, że czas, gdy w obudowie była tylko jedna struktura, powoli się kończy. Koszty rozwoju i ograniczenia w skalowaniu technologii krzemowej nie pozwalają na miniaturyzację poprzez coraz mniejszy wymiar charakterystyczny procesu. Chipy 3D omijają ograniczenia prawa Moore'a, stąd rozwiązania te nazywa się "More than Moore". Rozwiązania 3D bazujące na interposerze jako podłożu, na którym mocuje się i spiętrza struktury, mają jeszcze dwie zalety – modułowość i skalowalność. Zmiana czegokolwiek w SoC oznaczała konieczność wymiany masek i powtórki produkcji. W piętrowym układzie można będzie poprawić jedynie wadliwy element, a jeśli zostanie zostawione wolne miejsce, to niewielkim kosztem (bez udziału foundry) będzie można chipy customizować.

Robert Magdziak