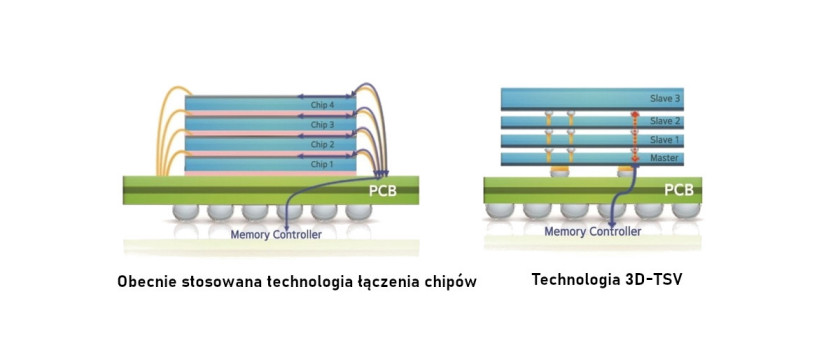

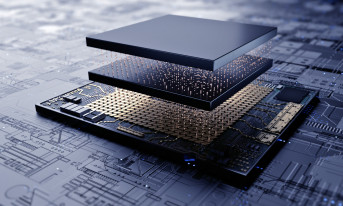

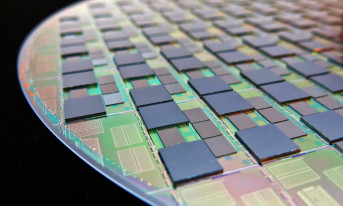

To rozwiązanie pozwoli firmom zaoferować produkty nowej generacji o znacznie większej pojemności i wydajności, bez potrzeby wprowadzania zmian do projektów. Ponadto technologia zamykania struktur półprzewodnikowych 3D zapewnia szybszą transmisję danych między chipami niż obecnie stosowane rozwiązanie polegające na łączeniu układów mikroprzewodami.

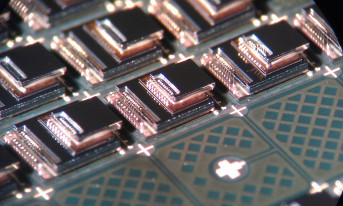

Poprzez zwiększenie liczby chipów ułożonych w stos z 8 do 12 warstw, Samsung będzie mógł wkrótce masowo wytwarzać układy HBM o pojemności 24 GB. Zapewni to trzykrotnie większą pojemność niż dostępne na rynku 8 GB pamięci o wysokiej przepustowości.

Źródło: Electronics Weekly