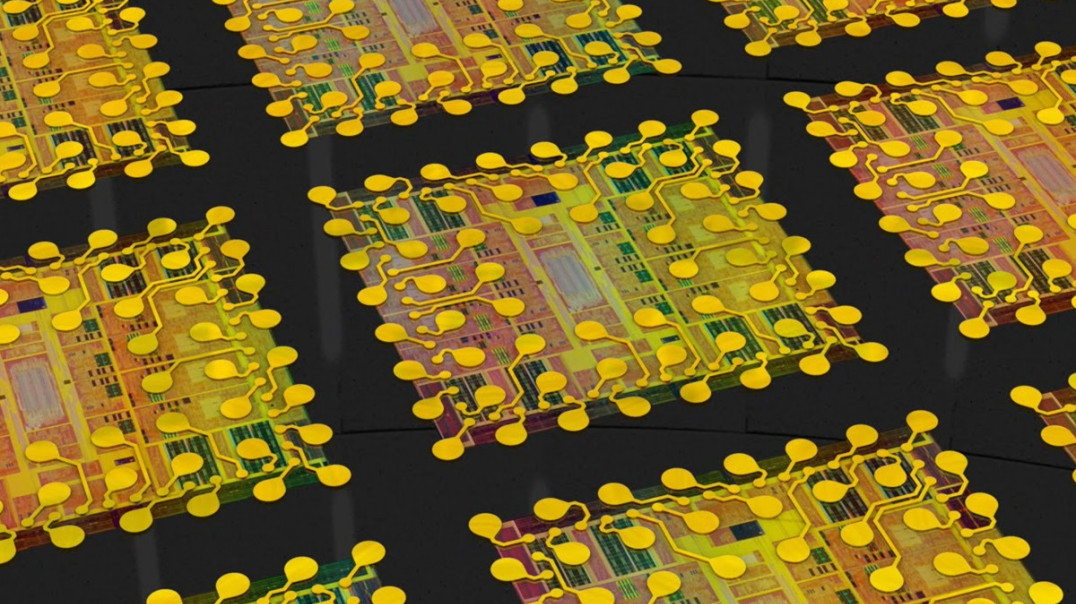

Dla obu układów tego typu można zaobserwować potrzebę zwiększania ich mocy obliczeniowej. Oczekuje się, że wzrost wykorzystania technologii fan-out przy produkcji chipów związanych z łącznością - w tym Bluetooth, a także MEMS, PA i switchy - osiągnie średni roczny poziom 14%. Zgodnie z prognozami, do 2025 roku przychód z pakowania chipów w technologii fan-out wyniesie 1,532 mln dolarów przy wskaźniku CAGR na poziomie 20,2%.

W tym czasie pojawią się nowe rozwiązania w sektorze HPC, co przyczyni się do wzrostu zapotrzebowania na zamykanie struktur półprzewodnikowych metodą fan-out UHD, która stanie się bardziej ekonomicznym rozwiązaniem w porównaniu do opakowań 2.5D.

Obecnie Samsung Electronics jest kluczowym producentem IDM na rynku, Powertech Technology wykorzystuje technologię FOPLP do pakowania struktur układów pamięci, a chiński JCET działa w sektorze OSAT (Outsourced Semiconductor Assembly and Test). Wszystkie wyżej wymienione podmioty zaczęły wykorzystywać technologię pakowania fan-out UHD w zamówieniach swoich klientów i jest to również częścią planu rozwojowego producentów.

Oczekuje się, że do 2025 roku przychody z opakowań fan-out typu HD osiągną 1,291 mln dolarów przy CAGR na poziomie 15,8%. Z drugiej strony, opakowania fan-out typu core utrzymają w latach 2019-2025 stabilny wzrost wynoszący 1%.

Pomimo tego, że przychody z technologii FOPLP i FOWLP wzrosną odpowiednio o 57 i 14% rocznie, to ostatnia wymieniona metoda zamykania struktur będzie w 2025 roku generować dwie trzecie łącznego przychodu w tym sektorze. Oczekuje się, że branża opakowań fan-out odzyska swoją dynamikę w 2021 roku.

Źródło: Electronics Weekly, Yole Developpement