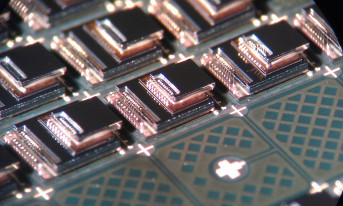

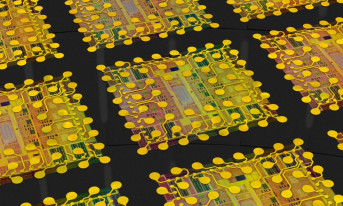

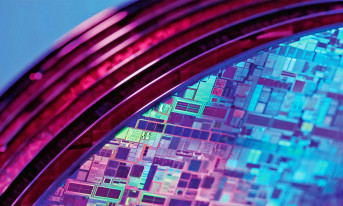

W technologii pakowania WLP struktury scalone są umieszczane w obudowach jeszcze przed ich wyodrębnieniem z płytki półprzewodnikowej. Zalicza się ją do grupy CSP (Chip-Scale Packaging), ponieważ obudowa jest praktycznie takiego samego rozmiaru, co struktura półprzewodnikowa. Jako alternatywa pakowania każdego układu scalonego niezależnie, po oddzieleniu go od pozostałych wykonanych w jednym cyklu produkcyjnym, metoda WLP ma wiele zalet. Przede wszystkim optymalizuje koszty i usprawnia proces produkcyjny oraz testowanie. Poza tym pozwala na wykonywanie mniejszych i cieńszych układów scalonych. Dzięki temu od lat zyskuje na popularności i jest wciąż udoskonalana przez wprowadzanie nowych wariantów.

Obudowy FIWLP

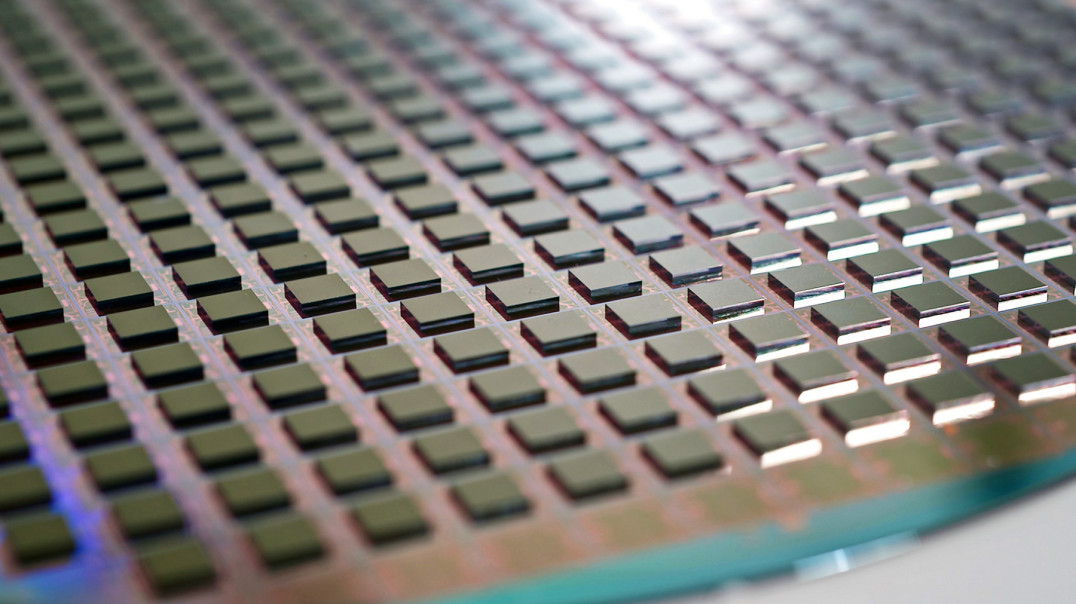

Zasadniczo wyróżnia się dwa warianty technologii pakowania WLP. Są to konstrukcje typu Fan-in (FI) oraz Fan-out (FO). W pierwszej z nich, tradycyjnej, jak opisaliśmy to we wstępie, obudowy są formowane na strukturach scalonych w ramach jeszcze niepodzielonej płytki półprzewodnikowej, dzięki czemu rozmiar struktury półprzewodnikowej i obudowy w zasadzie się pokrywają. Dopiero wówczas następuje wyodrębnienie poszczególnych układów. Obudowy typu Fan-In WLP (FIWLP) sprawdzają się w przypadku stosunkowo małej liczby wyprowadzeń.

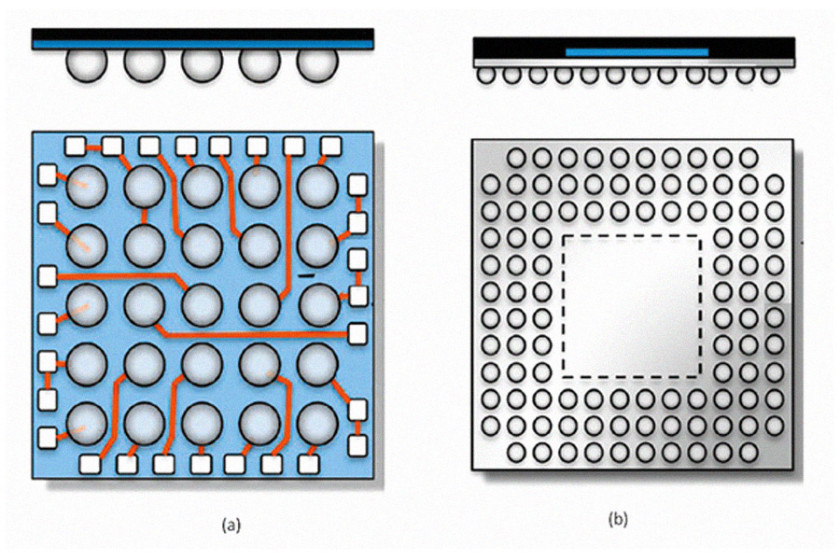

Technologię pakowania Fan-Out WLP (FOWLP)/Fan-Out Panel-Level Packaging (FOPLP) z kolei opracowano z myślą o układach scalonych wymagających większego poziomu integracji na mniejszej powierzchni oraz większej liczby wyprowadzeń. Oprócz tego obudowy FOWLP/FOPLP charakteryzują lepsze parametry termiczne i elektryczne, w porównaniu do obudów FIWLP.

Obudowy FOWLP

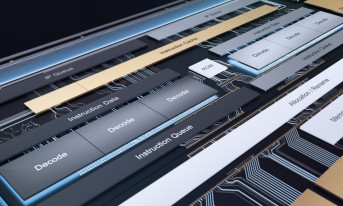

Zasadnicza różnica pomiędzy obudowami typu Fan-In WLP a obudowami typu FOWLP/FOPLP dotyczy sposobu włączenia do opakowania warstwy redystrybucyjnej (redistribution layer, RDL), w której prowadzone są połączenia wyprowadzeń struktury scalonej z wyprowadzeniami obudowy układu scalonego. W przypadku pierwszych warstwa redystrybucyjna pokrywa się z obrysem struktury scalonej. W drugich z kolei strukturę scaloną osadza się w materiale obudowy z zapasem, zaś dodatkowe miejsce wykorzystuje się na rozprowadzenie w nim połączeń w ramach warstwy redystrybucyjnej w taki sposób, że wykracza ona poza obrys struktury scalonej (rys. 1).

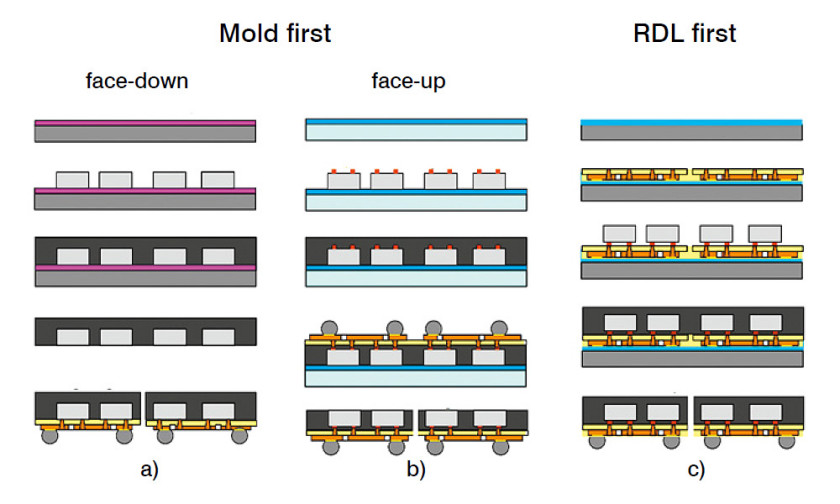

W produkcji obudów typu Fan-Out WLP/FOPLP praktykuje się dwa podejścia: mold first i RDL first. W pierwszym z nich wprowadza się dalszą klasyfikację, na procesy typu face down oraz face up. Wszystkie warianty są wykorzystywane w masowej produkcji układów scalonych. Na rysunku 2 przedstawiamy różnice między nimi.

Technika face down a face up

W produkcji obudów typu Fan-Out WLP/FOPLP metodą mold first w wariancie face down pierwszym etapem jest umieszczenie matrycy struktur scalonych na podłożu tymczasowym, pokrytym usuwalną termicznie taśmą. W kolejnym kroku następuje obtrysk tej matrycy tworzywem sztucznym. Następnie jest ona oddzielana od podłoża i wówczas wykonuje się, zwykle w technologii cienkowarstwowej, warstwę redystrybucyjną, którą łączy się z kontaktami obudowy (rys. 2a). Na koniec poszczególne układy scalone są wyodrębniane z matrycy.

W wariancie face up również rozpoczyna się od umieszczenia matrycy struktur scalonych na podłożu tymczasowym z warstwą klejącą, ale inaczej niż w wariancie face down układa się je kontaktami "w górę". Następnie wykonywany jest obtrysk tworzywem sztucznym. Aby uzyskać dostęp do wyprowadzeń struktury scalonej, tworzywo punktowo się zeszlifowuje. To pozwala na wykonanie warstwy redystrybucyjnej, którą łączy się z kontaktami obudowy. Na koniec podłoże tymczasowe jest usuwane (odklejane), a matryca jest rozcinana na poszczególne układy (rys. 2b).

Na czym polega metoda RDL first?

W produkcji obudów typu FOWLP / FOPLP metodą RDL first z kolei najpierw na podłożu tymczasowym z warstwą klejącą wykonuje się warstwę redystrybucyjną. Na niej umieszczana jest matryca struktur scalonych. Następnie wykonuje się jej obtrysk tworzywem sztucznym. W ostatnim kroku podłoże tymczasowe jest usuwane, wykonuje się kontakty obudowy i rozcina matrycą na oddzielne układy (rys. 2c). Specyfika przedstawionych technik pakowania powoduje różnice w wykonaniu obudów różnych typów.

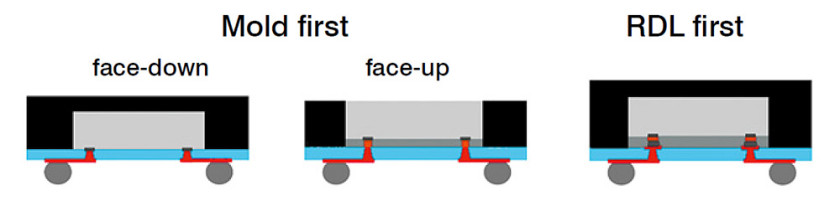

W podejściu mold first face down uzyskiwane są najkrótsze połączenie między wyprowadzeniami struktury scalonej a kontaktami obudowy, co jest ważne szczególnie w przypadku sygnałów o dużych częstotliwościach. Ponadto w technice mold first face-up, jak i w podejściu RDL first pomiędzy strukturą scaloną a warstwą redystrybucyjną znajduje się dodatkowa warstwa tworzywa sztucznego (rys. 3), co negatywnie odbija się na parametrach elektrycznych oraz niezawodności układu.

Monika Jaworowska