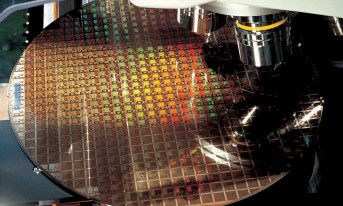

- Nasz rozwój technologii 3 nm przebiega zgodnie z planem. Obserwujemy znacznie wyższy poziom zaangażowania klientów, zarówno w przypadku aplikacji HPC, jak i smartfonów, w porównaniu z 5 i 7 nm - powiedział CEO TSMC CC Wei podczas konferencji dotyczącej wyników firmy.

TSMC wyznaczyło również cel inwestycyjny opiewający na kwotę 25-28 mld dolarów. Jest on znacznie wyższy w porównaniu do kwoty 20-22 mld dolarów oszacowanej przez obserwatorów rynku.

- Poziom nakładów inwestycyjnych TSMC pozostaje wysoki ze względu na złożoność technologii - powiedział CEO, odpowiadając na pytania podczas konferencji. Wydatki TSMC na sprzęt produkcyjny EUV w związku z rozwojem technologii, są jednym z powodów wyższych nakładów inwestycyjnych w tym roku.

Według TSMC wyższy poziom wykorzystania mocy produkcyjnych jest konieczny, aby zwiększyć przyszłe możliwości wzrostu. Firma podniosła cel wskaźnika CAGR do 10-15 % w zakresie przychodów w USD do 2025 roku. Ponadto TSMC ujawniło, że technologia pakowania 3D SoIC (system-on-integrated chips) będzie gotowa do wykorzystania w produkcji w 2022 roku. Technologia SoIC TSMC zostanie po raz pierwszy przyjęta do zastosowań w aplikacjach HPC.

Tajwański gigant szacuje, że przychody z usług deweloperskich będą rosły w tempie wyższym niż średnia korporacyjna w ciągu najbliższych kilku lat. TSMC promuje rodzinę technologii 3DFabric, składającą się z CoWoS i InFO 3D stacking foundry oraz SoIC do heterogenicznej integracji układów 3D.

Źródło: Digitimes